Huaicheng Li<sup>\*</sup>\*, Martin L. Putra<sup>\*</sup>, Ronald Shi<sup>\*</sup>, Xing Lin<sup>\*</sup>, Gregory R. Ganger<sup>\*</sup>, Haryadi S. Gunawi <sup>\*</sup>

The 28th ACM Symposium on Operating Systems Principles (SOSP'21)

\*University of Chicago, \*Carnegie Mellon University, \*NetApp

"Small but powerful"

"Small but powerful"

"Small but powerful"

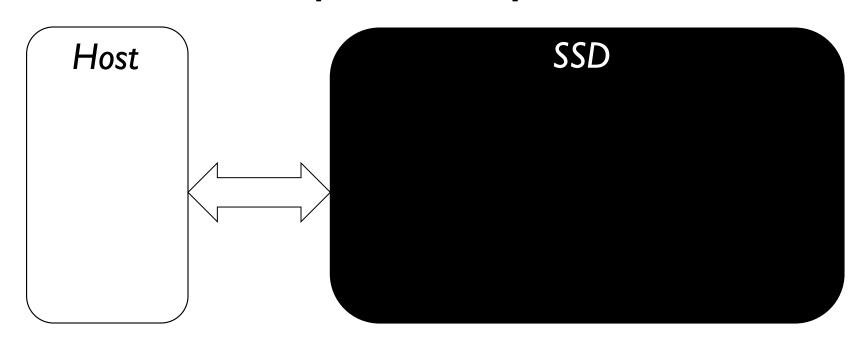

Host

SSD0 SSD1 SSD2 SSD3

SSD0 SSD1 SSD2 SSD3

SSD0 SSD1 SSD2 SSD3

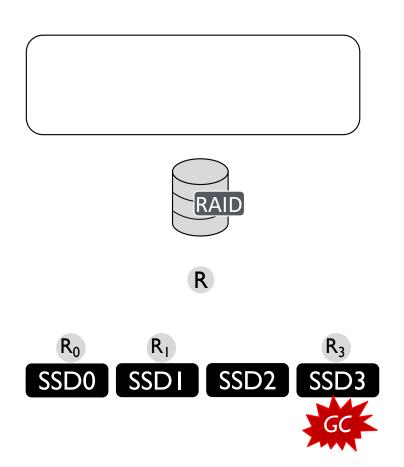

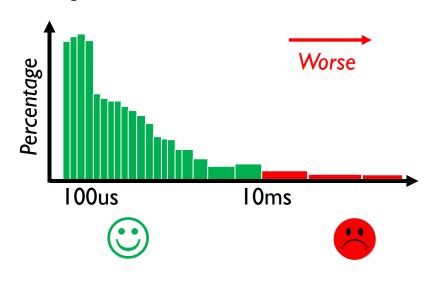

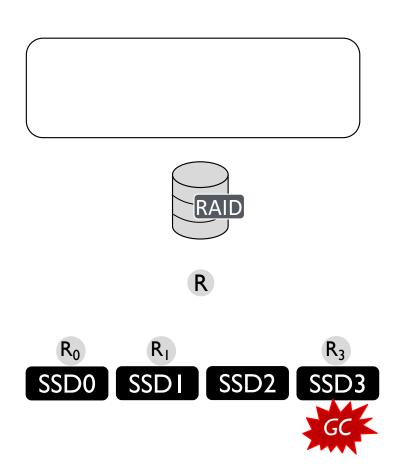

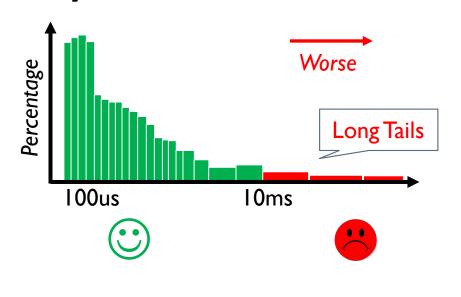

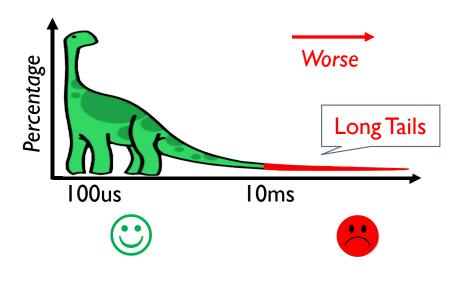

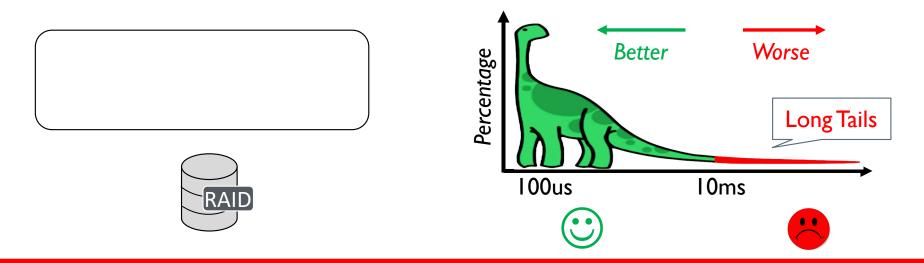

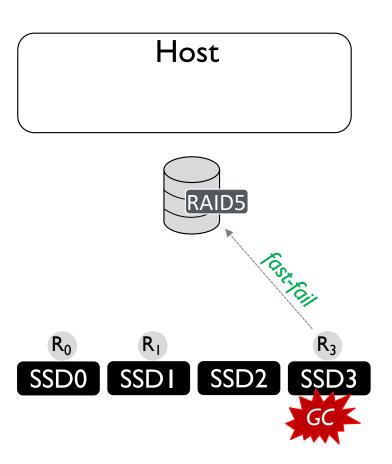

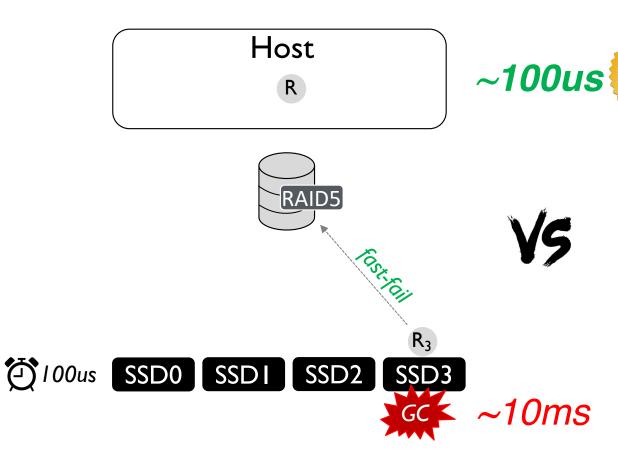

# A slow SSD makes the entire flash array slow!

# "A New Hope" - NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

# "A New Hope" – NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

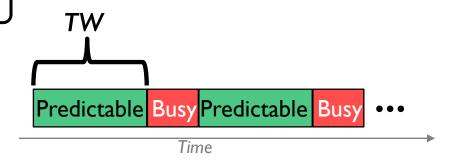

A major leap

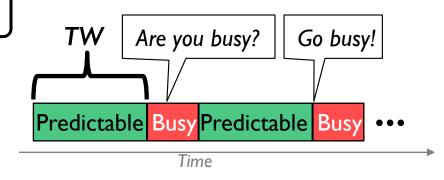

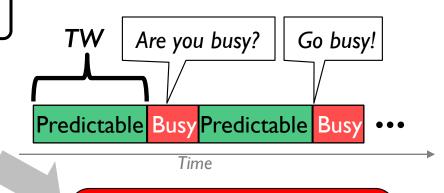

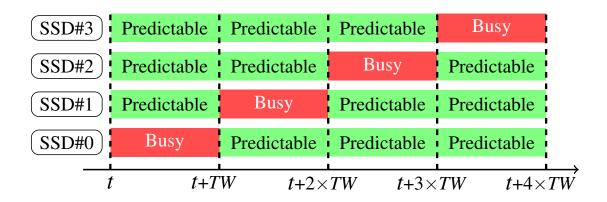

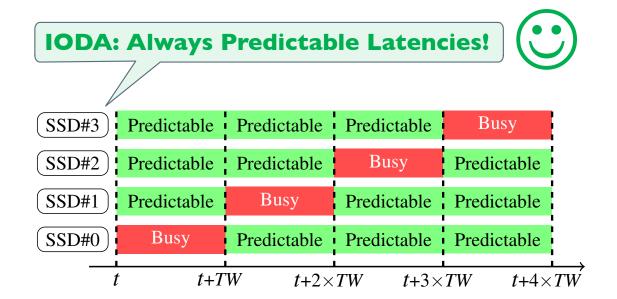

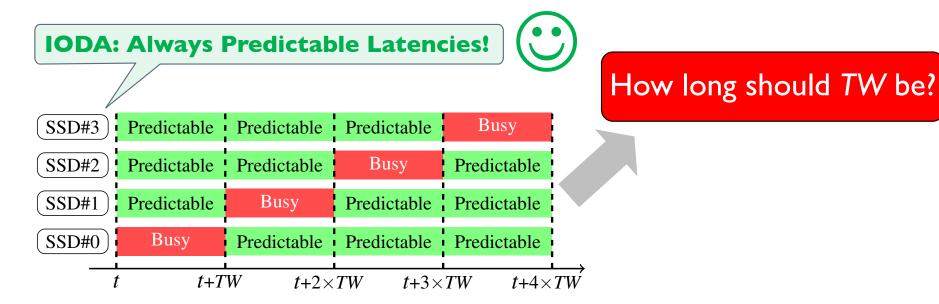

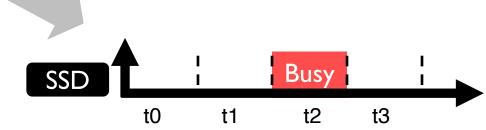

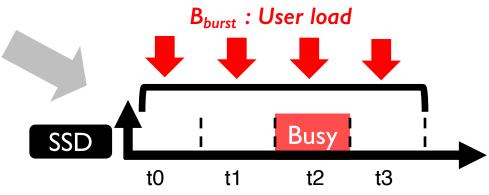

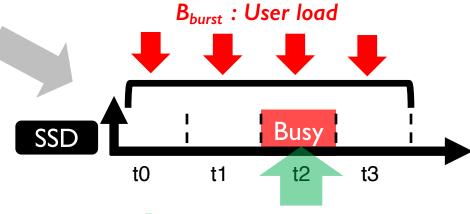

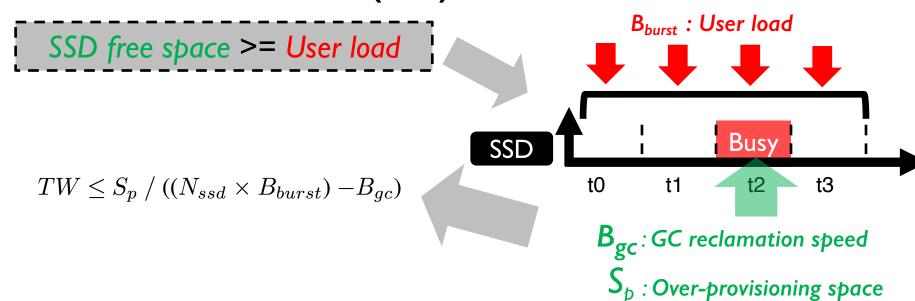

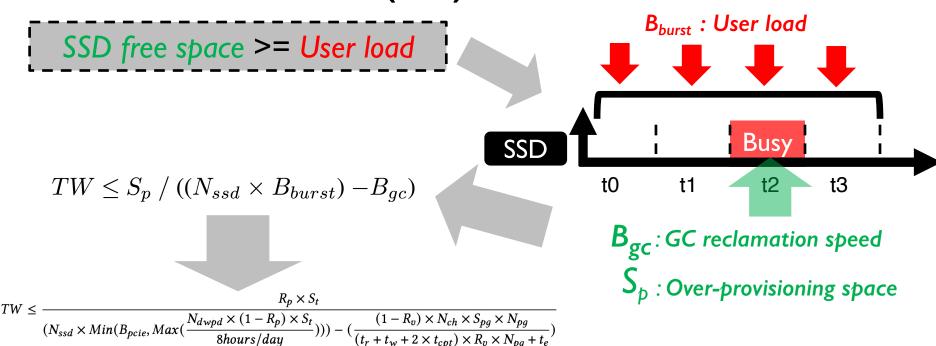

- Predictable/Busy Time Window (TW)

- Device status query & toggling

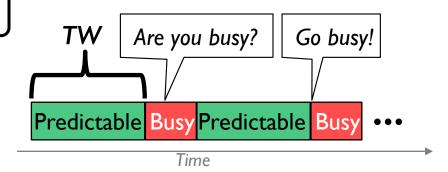

# "A New Hope" - NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

A major leap

- Predictable/Busy Time Window (TW)

- Device status query & toggling

# "A New Hope" – NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

A major leap

- Predictable/Busy Time Window (TW)

- Device status query & toggling

# "A New Hope" - NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

A major leap

- Predictable/Busy Time Window (TW)

- Device status query & toggling

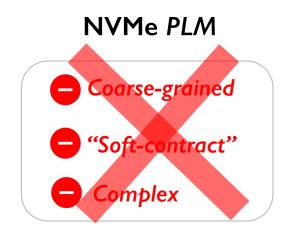

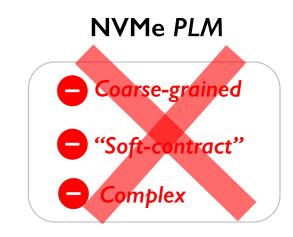

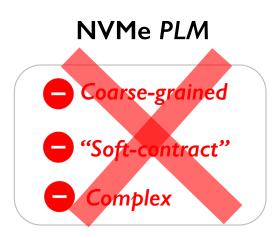

But insufficient

- Coarse-grained device-level predictability

- General Contract Transfer of the Contract Tran

- Requiring complex status tracking

# "A New Hope" – NVMe Predictable Latency Mode

NVMe Predictable Latency Mode (**PLM**)

A major leap

- Predictable/Busy Time Window (TW)

- Device status query & toggling

But insufficient

- Coarse-grained device-level predictability

- "Soft-contract" breaking predictability

- Requiring complex status tracking

- **—** ····

How to leverage NVMe PLM and enhance it for predictable latencies?

☐ Goal: Tail-free flash array system on top of slightly-extended PLM interface

- ☐ Goal: Tail-free flash array system on top of slightly-extended PLM interface

- ☐ Design Principles:

- **Simple** policies for efficiency

- Minimal changes for easy deployment

- ☐ Goal: Tail-free flash array system on top of slightly-extended PLM interface

- Design Principles:

- **Simple** policies for efficiency

- Minimal changes for easy deployment

- ☐ IODA Approach/Techniques:

- ☐ Goal: Tail-free flash array system on top of slightly-extended PLM interface

- ☐ Design Principles:

- **Simple** policies for efficiency

- Minimal changes for easy deployment

- ☐ IODA Approach/Techniques:

- + Per-I/O latency predictability

- **★** Busy Remaining Time (BRT) Exposure

- ☐ Goal: Tail-free flash array system on top of slightly-extended PLM interface

- Design Principles:

- **Simple** policies for efficiency

- Minimal changes for easy deployment

- ☐ IODA Approach/Techniques:

- + Per-I/O latency predictability

- **★** Busy Remaining Time (BRT) Exposure

- **Time Window** (TW) Formulation

- Goal: Tail-free flash array system on top of slightly-extended PLM interface

- Design Principles:

- **Simple** policies for efficiency

- Minimal changes for easy deployment

- ☐ IODA Approach/Techniques:

- ♣ Per-I/O latency predictability

- → Busy Remaining Time (BRT) Exposure

- **Time Window** (TW) Formulation

- + An end-to-end design exploiting above extensions

- □ Background & Motivation

- □ IODA Overview

- □ IODA Design

- Predictable latency flagged I/Os

- Busy remaining time

- Time window formulation

- Relaxed TW for better write amplification

- □ Evaluation

- □ Summary

## Leverage Redundancy for Performance

An old, effective idea;

### An old, effective idea; Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs Trimming the Tail for Deterministic Read Performance in SSDs Latency Reduction and Load Balancing in Coded Storage Systems RAIL: Predictable, Low Tail Latency for NVMe MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding K. V. Rashmi<sup>1</sup>, Mosharaf Chowdhury<sup>2</sup>, Jack Kosaian<sup>2</sup>, Ion Stoica<sup>1</sup>, Kannan Ramchandran<sup>1</sup> 1 UC Berkeley 2 University of Michigan Data-intensive clusters and object stores are increasingly relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the Object A of size A challenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance. tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using craeach of size A/k EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs Figure 1: EC-Cache splits individual objects and encodes them erasure coding by: (i) splitting and erasure coding inusing an crasure code to enable read parallelism and late binddividual objects during writes, and (ii) late binding, ing during individual reads. wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective replication, EC-Cache improves load balancing by more pling [12, 16, 52] and compression [15, 27, 53, 79] are than 3× and reduces the median and tail read latencies some of the popular approaches employed to increase the by more than 2×, while using the same amount of memeffective memory capacity. (iii) Ensuring good I/O perory. EC-Cache does so using 10% additional bandwidth formance for the cached data in the presence of skewed and a small increase in the amount of stored metadata. The heavily offered by FC Cache are further amplified. The heavily offered by FC Cache are further amplified.

The benefits offered by EC-Cache are further amplified

in the presence of background network load imbalance are heavily skewed [20, 47], and this creates signifi-

Typically, the popularity of objects in cluster caches

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

> EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding

K. V. Rashmi<sup>1</sup>, Mosharaf Chowdhury<sup>2</sup>, Jack Kosaian<sup>2</sup>, Ion Stoica<sup>1</sup>, Kannan Ramchandran<sup>1</sup> 1 UC Berkeley 2 University of Michigan

Data-intensive clusters and object stores are increasingly relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the challenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance. tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using cra-

EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs Figure 1: EC-Cache splits individual objects and encodes them erasure coding by: (i) splitting and erasure coding individual objects during writes, and (ii) late binding. wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective replication, EC-Cache improves load balancing by more pling [12, 16, 52] and compression [15, 27, 53, 79] are than 3× and reduces the median and tail read latencies by more than 2×, while using the same amount of memory. EC-Cache does so using 10% additional bandwidth and a small increase in the amount of stored metadata The benefits offered by EC-Cache are further amplified in the presence of background network load imbalance are heavily skewed [20, 47], and this creates signifi-

some of the popular approaches employed to increase the formance for the cached data in the presence of skewed popularity, background load imbalance, and failures. Typically, the popularity of objects in cluster caches

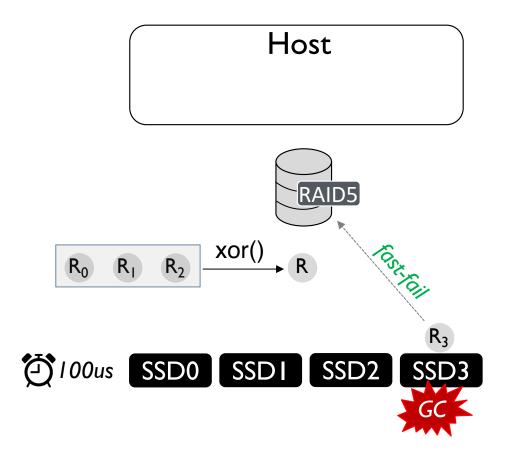

An old, effective idea; Yet, challenging for PLM

When to issue the parity reads?

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

> EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding

K. V. Rashmi1, Mosharaf Chowdhury2, Jack Kosaian2, Ion Stoica1, Kannan Ramchandran 1 UC Berkeley 2 University of Michigan

Data-intensive clusters and object stores are increasingly relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the challenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance. tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using cra-

EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs erasure coding by: (i) splitting and erasure coding individual objects during writes, and (ii) late binding, wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective replication, EC-Cache improves load balancing by more pling [12, 16, 52] and compression [15, 27, 53, 79] are than 3× and reduces the median and tail read latencies ory. EC-Cache does so using 10% additional bandwidth and a small increase in the amount of stored metadata The benefits offered by EC-Cache are further amplified

using an crasure code to enable read parallelism and late binding during individual reads.

some of the popular approaches employed to increase the by more than 2×, while using the same amount of memformance for the cached data in the presence of skewed popularity, background load imbalance, and failures. Typically, the popularity of objects in cluster caches in the presence of background network load imbalance are heavily skewed [20, 47], and this creates signifi-

## An old, effective idea; Yet, challenging for PLM

When to issue the parity reads?

(1) Wait for timeout

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

> EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding

K. V. Rashmi1, Mosharaf Chowdhury2, Jack Kosaian2, Ion Stoica1, Kannan Ramchandran 1 UC Berkeley 2 University of Michigan

Data-intensive clusters and object stores are increasingly relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the challenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance. tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using cra-

EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs erasure coding by: (i) splitting and erasure coding individual objects during writes, and (ii) late binding. wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective replication, EC-Cache improves load balancing by more pling [12, 16, 52] and compression [15, 27, 53, 79] are than 3× and reduces the median and tail read latencies by more than 2x, while using the same amount of memory. EC-Cache does so using 10% additional bandwidth and a small increase in the amount of stored metadata The benefits offered by EC-Cache are further amplified

Figure 1: EC-Cache splits individual objects and encodes them using an erasure code to enable read parallelism and late binding during individual reads.

some of the popular approaches employed to increase the effective memory capacity. (iii) Ensuring good I/O performance for the cached data in the presence of skewed popularity, background load imbalance, and failures. Typically, the popularity of objects in cluster caches in the presence of background network load imbalance are heavily skewed [20, 47], and this creates signifi-

An old, effective idea; Yet, challenging for PLM

When to issue the parity reads?

(1) Wait for timeout

Best threshold? Tricky

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

> EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding

K. V. Rashmi1, Mosharaf Chowdhury2, Jack Kosaian2, Ion Stoica1, Kannan Ramchandran 1 UC Berkeley 2 University of Michigan

Data-intensive clusters and object stores are increasing relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the hallenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using era-

EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs erasure coding by: (i) splitting and erasure coding individual objects during writes, and (ii) late binding, wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective eplication, EC-Cache improves load balancing by more than 3× and reduces the median and tail read latencies by more than 2×, while using the same amount of memory. EC-Cache does so using 10% additional bandwidth and a small increase in the amount of stored metadata The benefits offered by EC-Cache are further amplified

in the presence of background network load imbalance

Figure 1: EC-Cache splits individual objects and encodes them using an erasure code to enable read parallelism and late binding during individual reads.

pline [12, 16, 52] and compression [15, 27, 53, 79] are some of the popular approaches employed to increase the effective memory capacity. (iii) Ensuring good I/O performance for the cached data in the presence of skewed popularity, background load imbalance, and failures. Typically, the popularity of objects in cluster caches

### An old, effective idea; Yet, challenging for PLM

When to issue the parity reads?

(1) Wait for timeout

Best threshold? Tricky

(2) Always Proactive (always send full-stripe)

### An old, effective idea; Yet, challenging for PLM

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

> EC-Cache: Load-balanced, Low-latency Cluster Caching with Online Erasure Coding

K. V. Rashmi1, Mosharaf Chowdhury2, Jack Kosaian2, Ion Stoica1, Kannan Ramchandran 1 UC Berkeley 2 University of Michigan

Data-intensive clusters and object stores are increasing relying on in-memory object caching to meet the I/O performance demands. These systems routinely face the hallenges of popularity skew, background load imbalance, and server failures, which result in severe load imbalance across servers and degraded I/O performance. tackle these challenges, where the number of cached replicas of an object is proportional to its popularity. In this paper, we explore an alternative approach using cra-

EC-Cache is a load-balanced, low latency cluster cache that uses online erasure coding to overcome the limitations of selective replication. EC-Cache employs erasure coding by: (i) splitting and erasure coding individual objects during writes, and (ii) late binding, wherein obtaining any k out of (k + r) splits of an object are sufficient, during reads. As compared to selective eplication, EC-Cache improves load balancing by more than 3× and reduces the median and tail read latencies by more than 2×, while using the same amount of memory. EC-Cache does so using 10% additional bandwidth and a small increase in the amount of stored metadata The benefits offered by EC-Cache are further amplified in the presence of background network load imbalance

pline [12, 16, 52] and compression [15, 27, 53, 79] are some of the popular approaches employed to increase the effective memory capacity. (iii) Ensuring good I/O performance for the cached data in the presence of skewed popularity, background load imbalance, and failures. Typically, the popularity of objects in cluster caches

When to issue the parity reads?

(1) Wait for timeout

Best threshold? Tricky

(2) Always Proactive (always send full-stripe)

☐ Increased load → Inefficient

Tiny-Tail Flash: Near-Perfect Elimination of Garbage Collection Tail Latencies in NAND SSDs

Trimming the Tail for Deterministic Read Performance in SSDs

Latency Reduction and Load Balancing in Coded Storage Systems

RAIL: Predictable, Low Tail Latency for NVMe

MittOS: Supporting Millisecond Tail Tolerance with Fast Rejecting SLO-Aware OS Interface

### An old, effective idea; Yet, challenging for PLM

When to issue the parity reads?

(1) Wait for timeout

Best threshold? Tricky

(2) Always Proactive (always send full-stripe)

Increased load → Inefficient

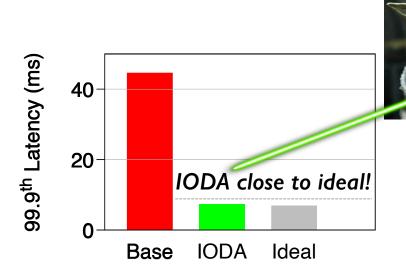

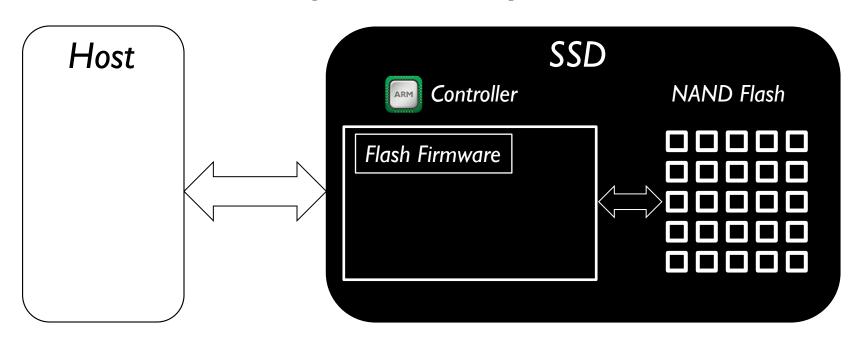

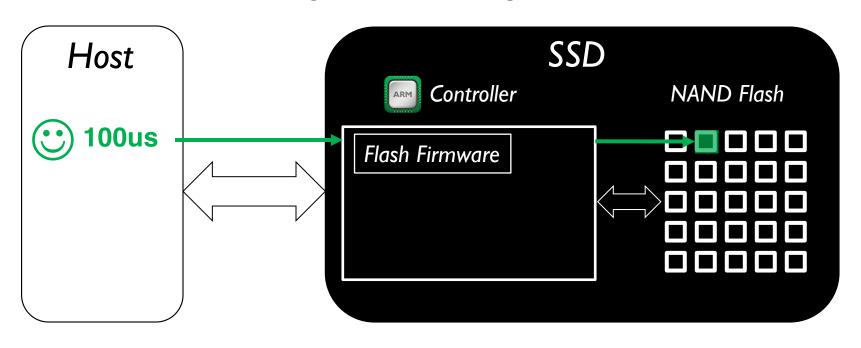

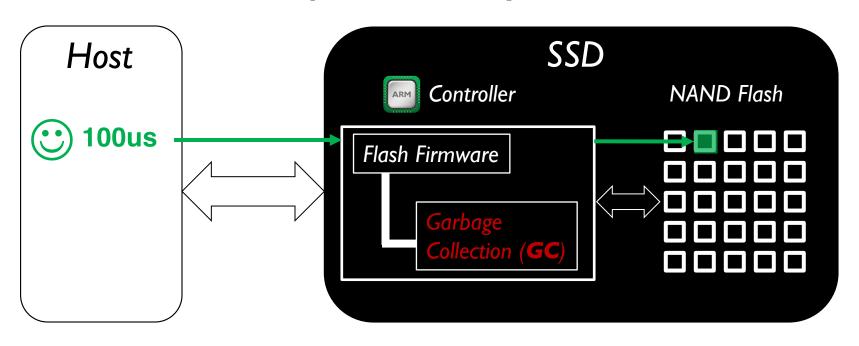

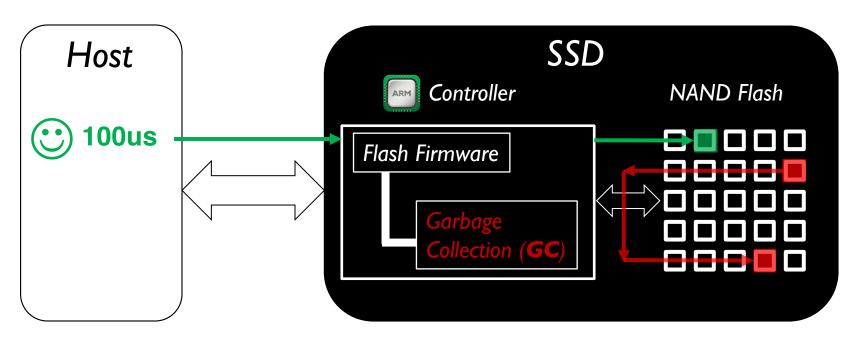

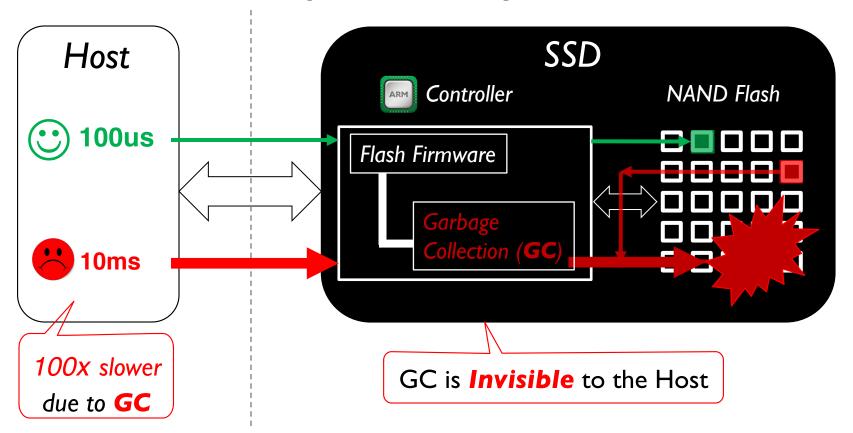

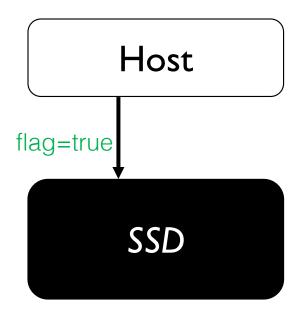

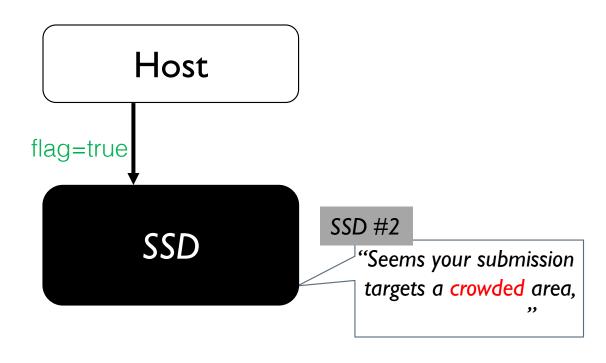

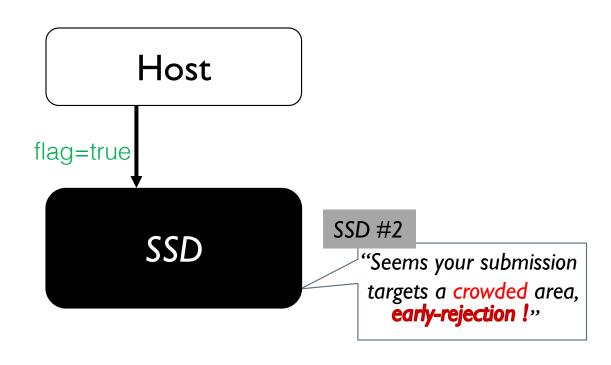

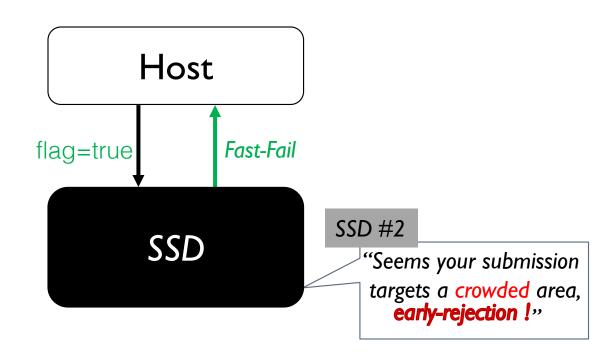

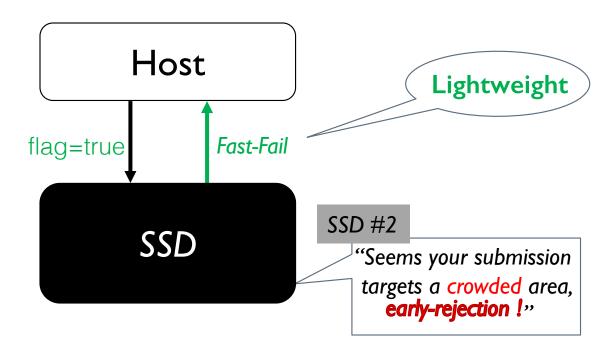

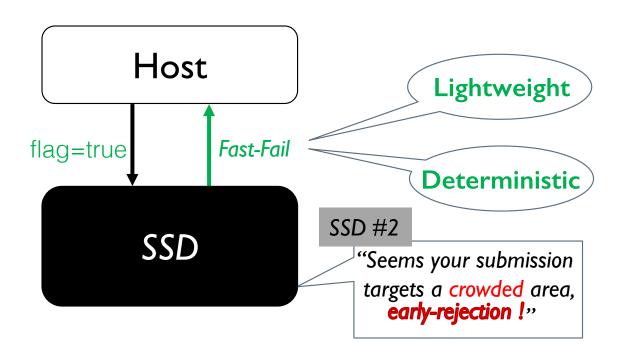

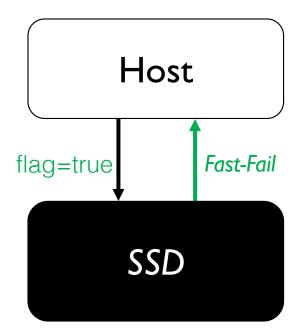

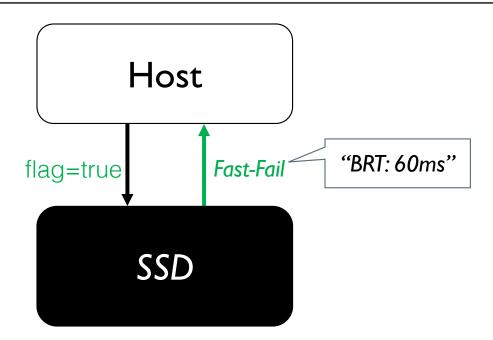

### Semantic gap between the Host and SSD to communicate the "busyness"

Host

SSD

Host

SSD0 SSD1 SSD2 SSD3

Host

RAID5

SSD0 SSD1 SSD2 SSD3

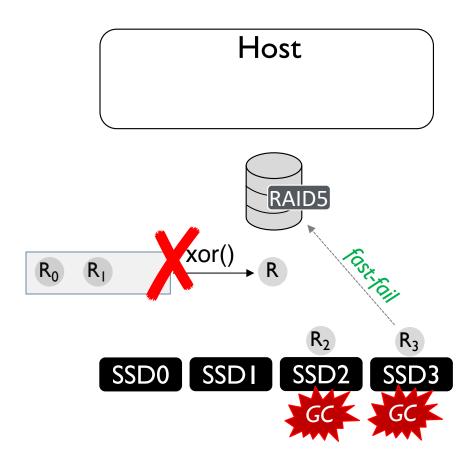

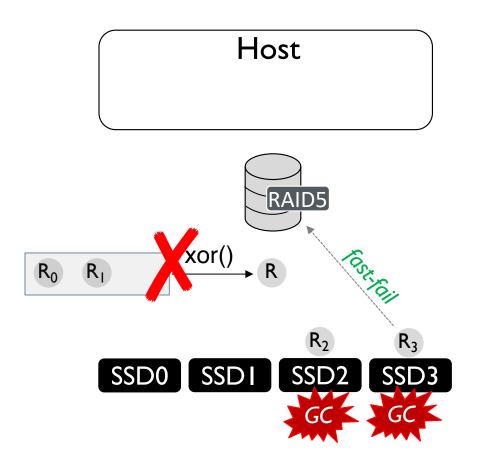

## A Case Against Proactive Reconstruction

SSD0 SSD1 SSD2 SSD3

## A Case Against Proactive Reconstruction

## A Case Against Proactive Reconstruction

Semantic Gap: the host doesn't know how long SSD "busyness" will last

## A Case Against Proactive Reconstruction

Semantic Gap: the host doesn't know how long SSD "busyness" will last

End up waiting for the busiest SSD

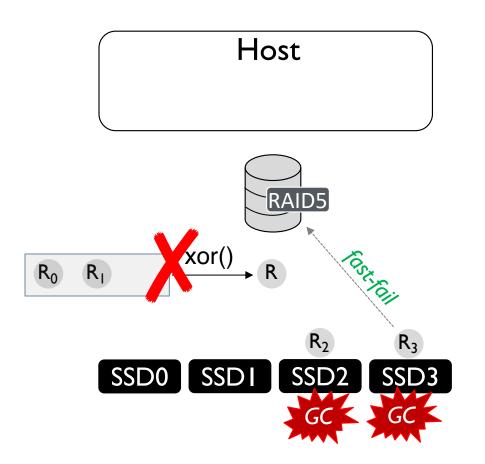

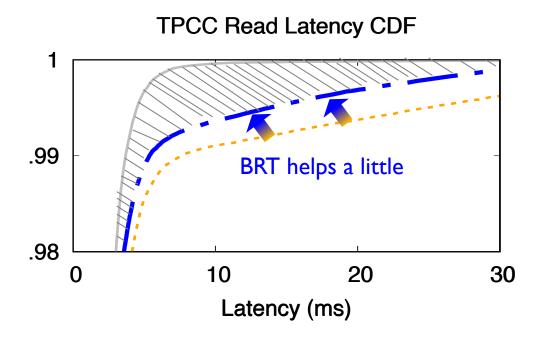

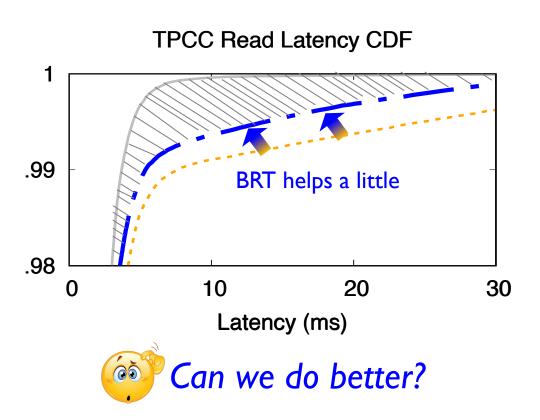

## Busy Remaining Time (BRT) Exposure

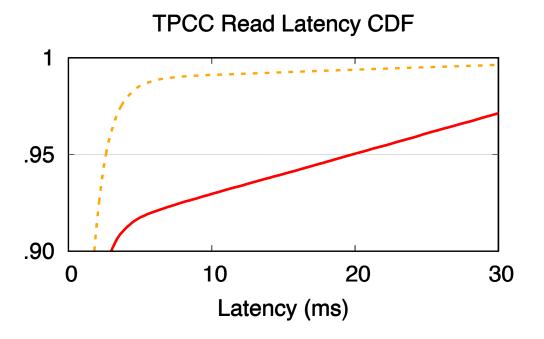

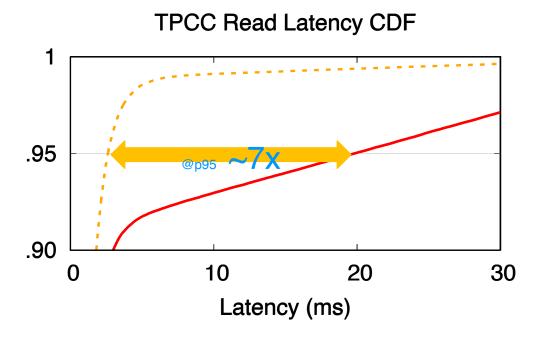

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

Piggybacking **BRT** to reconstruct data from less busy SSDs

## Busy Remaining Time (BRT) Exposure

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

Piggybacking BRT to reconstruct data from less busy SSDs

## Busy Remaining Time (BRT) Exposure

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

Piggybacking BRT to reconstruct data from less busy SSDs

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

"Fail-if-Slow": the SSD should fast-fail an I/O if it contends with GC

```

SSD free space >= User load

```

SSD free space >= User load

SSD free space >= User load

SSD free space >= User load

$B_{gc}$ : GC reclamation speed

$S_p$ : Over-provisioning space

TW Upper Bound

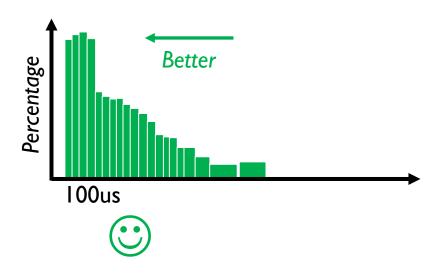

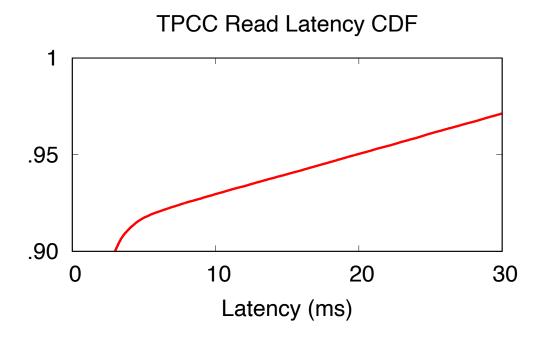

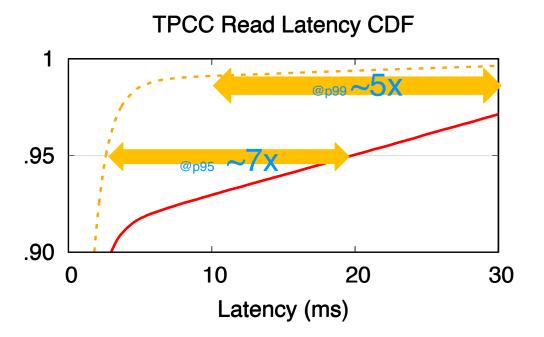

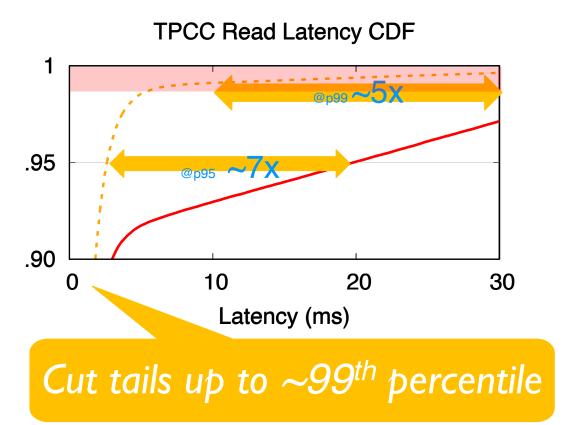

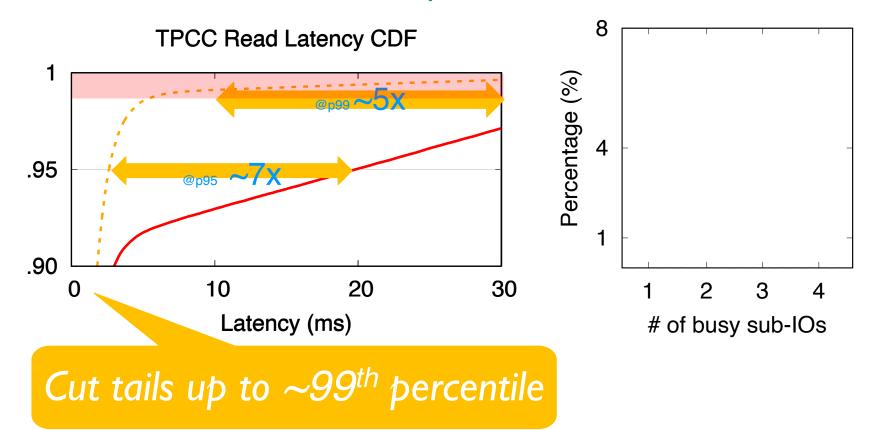

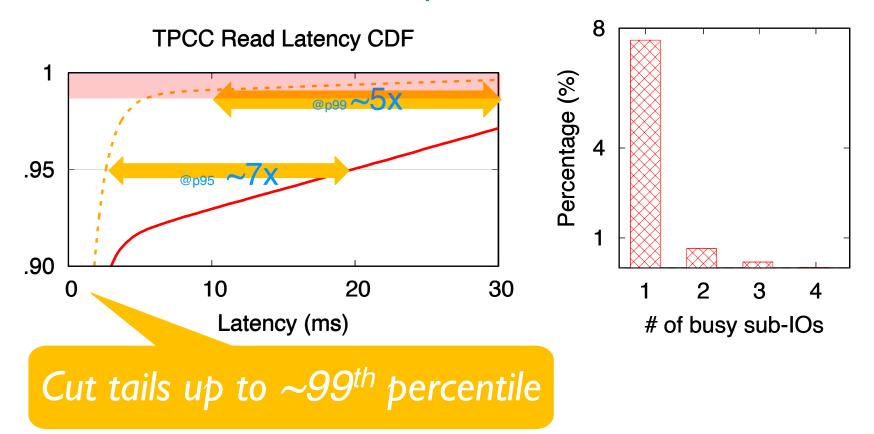

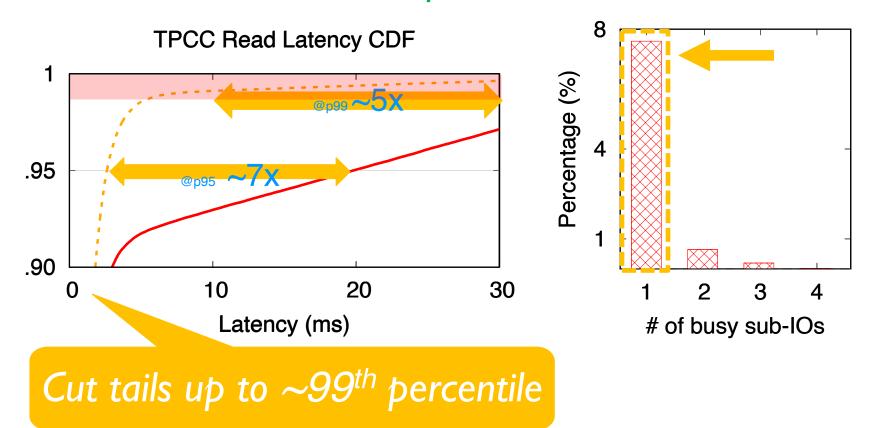

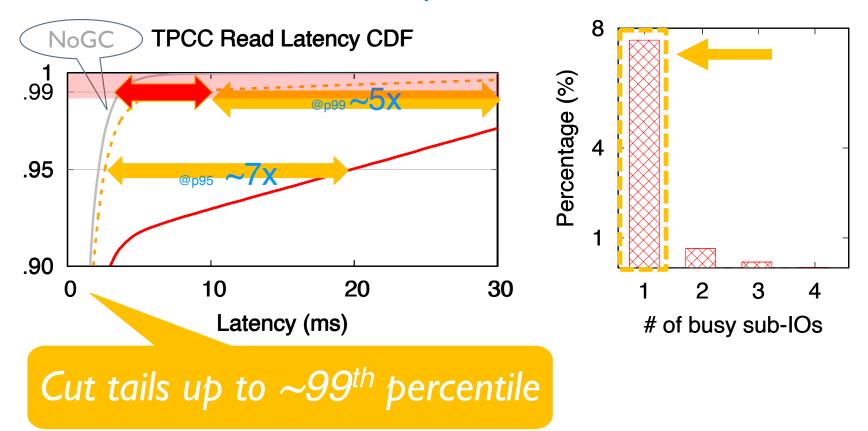

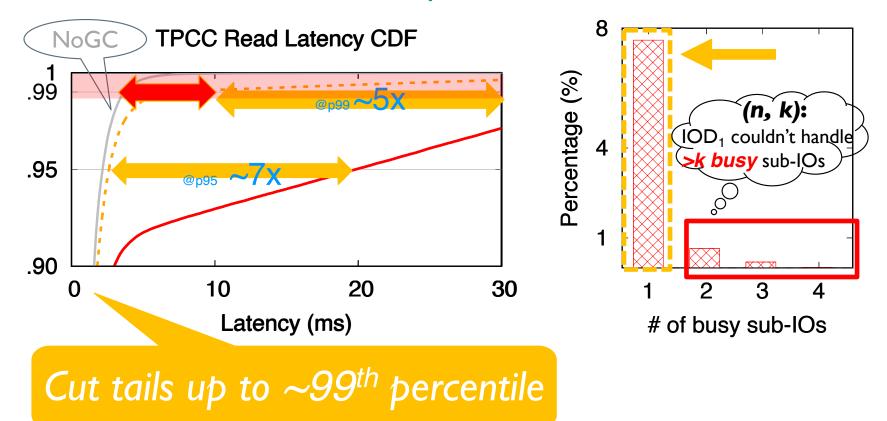

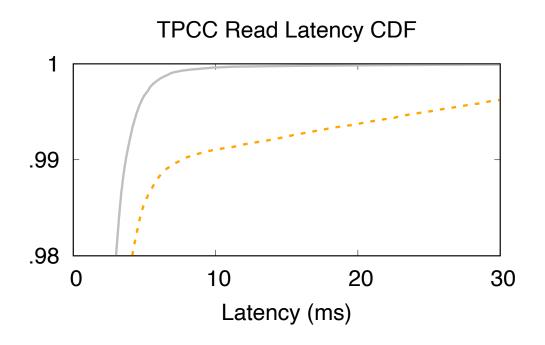

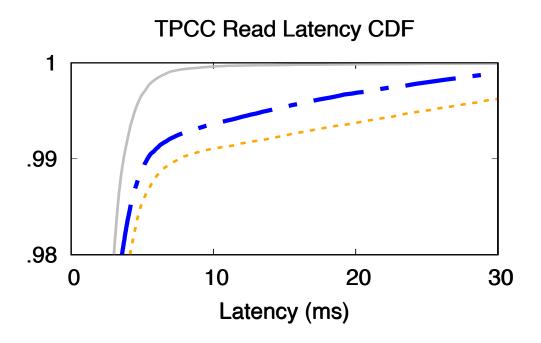

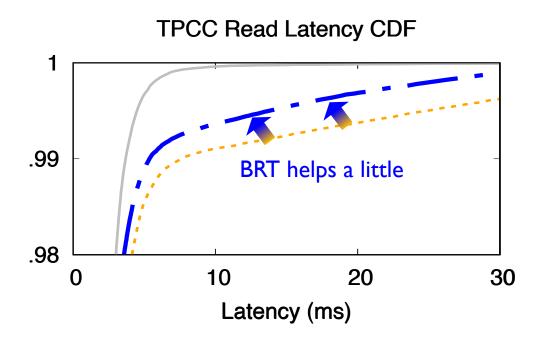

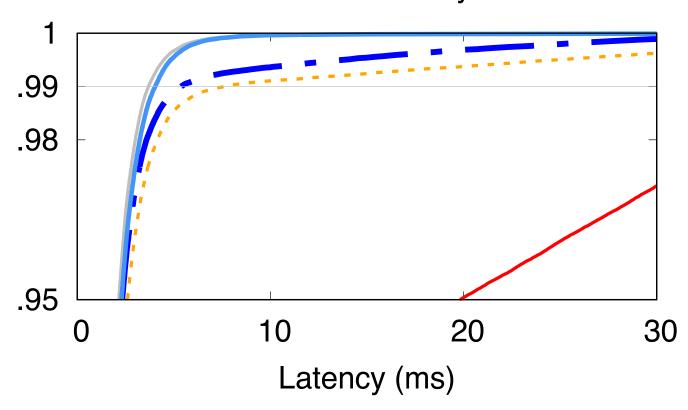

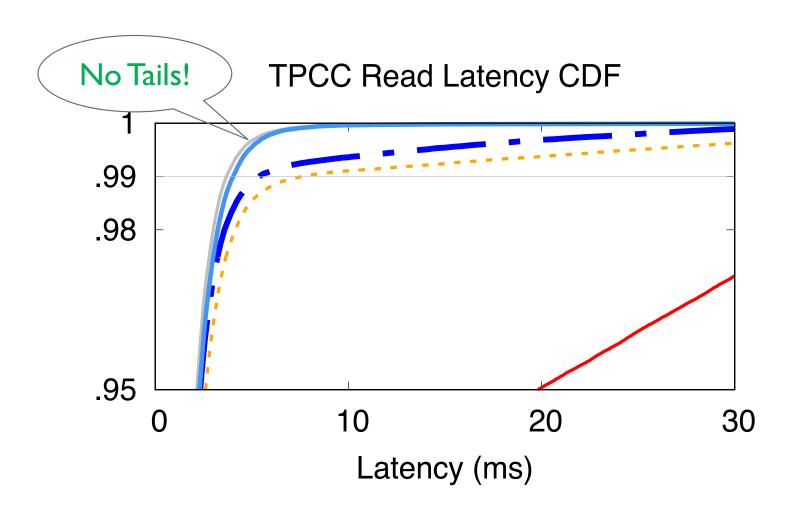

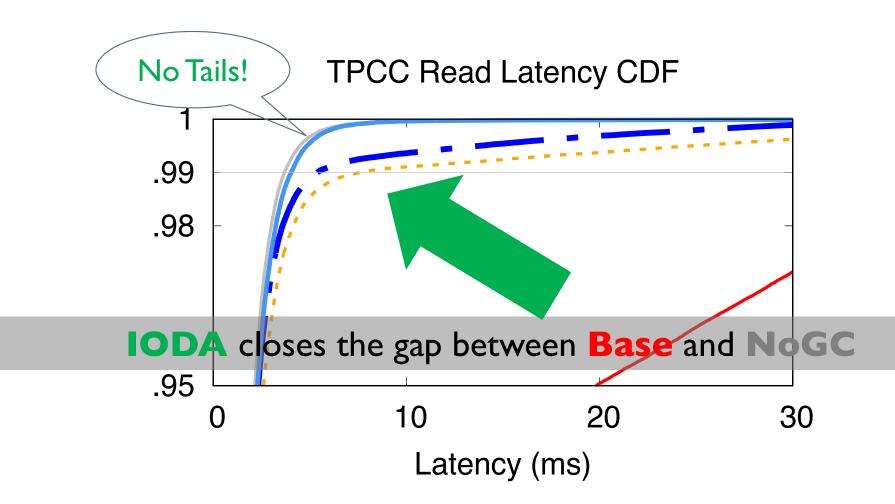

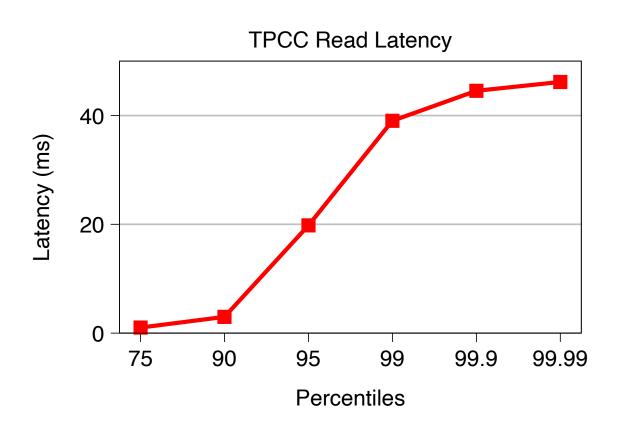

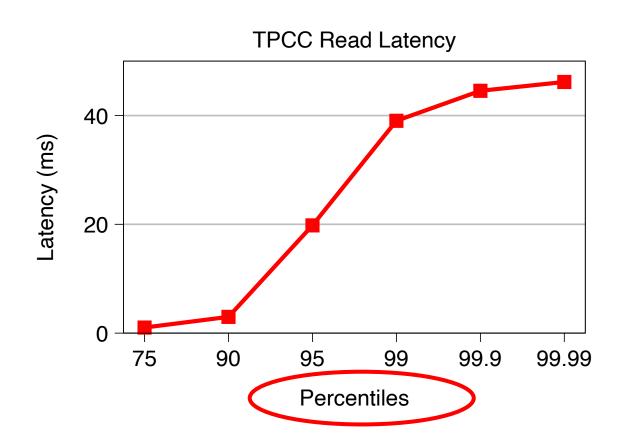

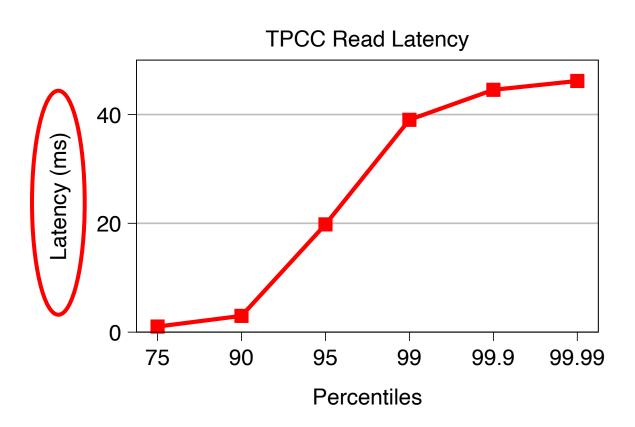

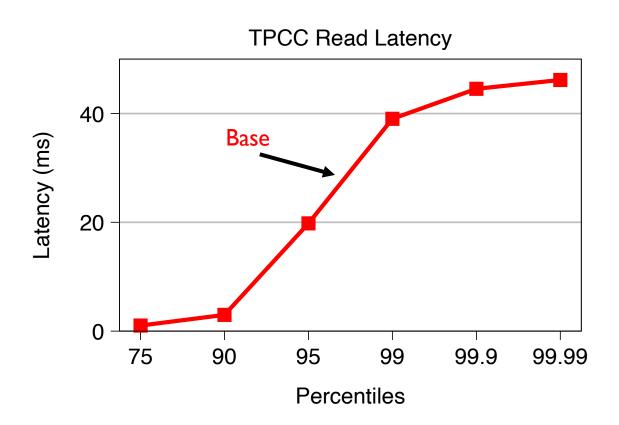

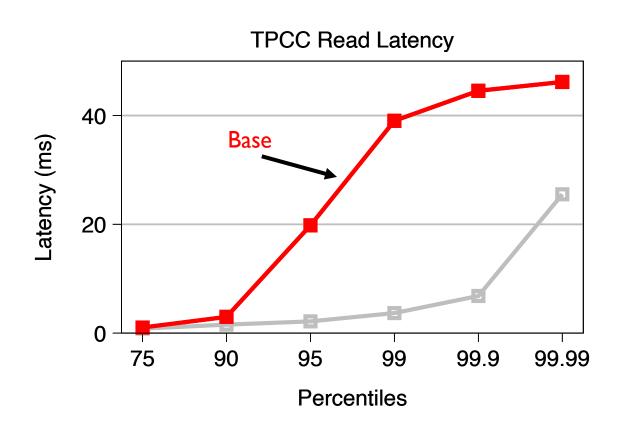

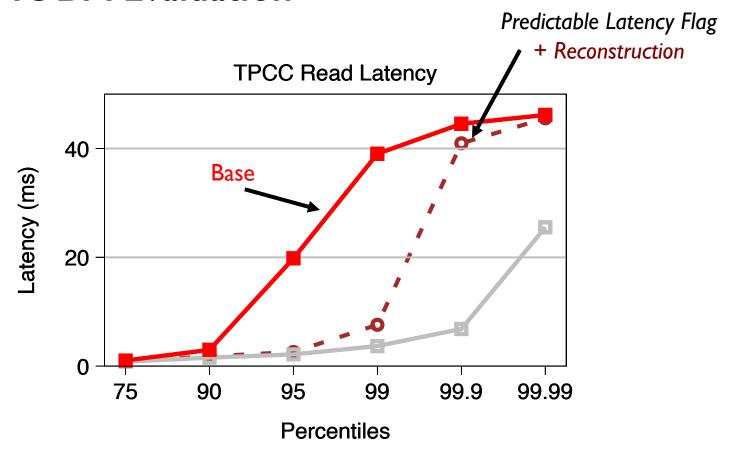

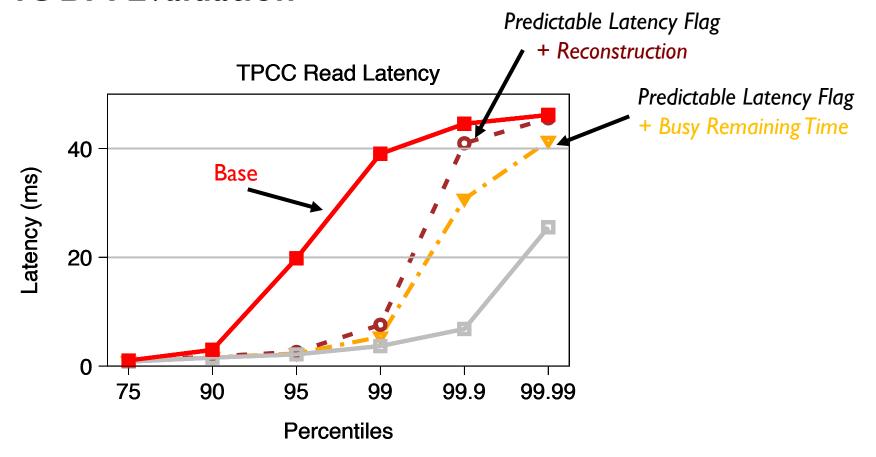

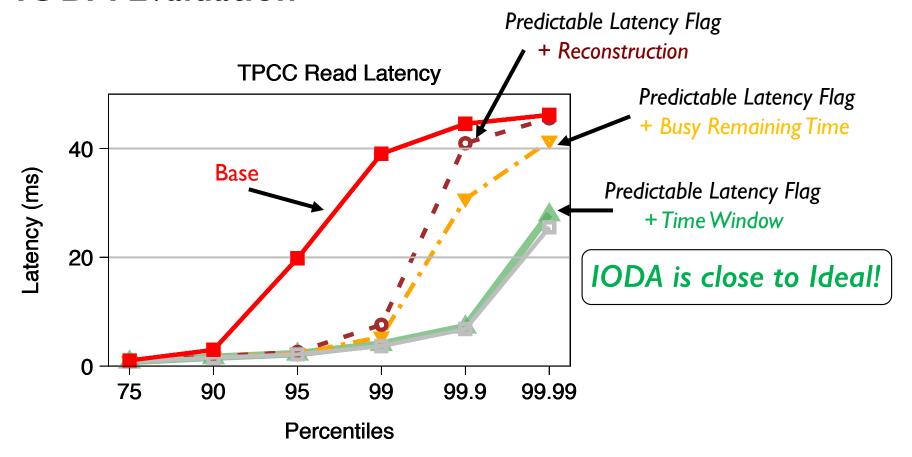

### TPCC Read Latency CDF

## More in the paper!

- □ IODA *TW* analysis

- 6 SSD models

- Relaxed TW

- TW vs.WAF tradeoffs

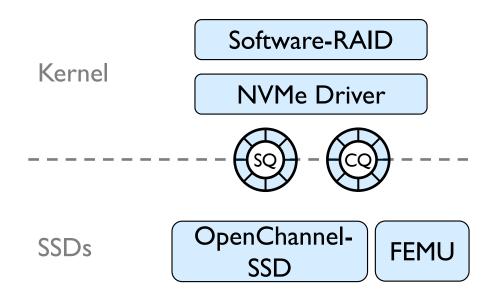

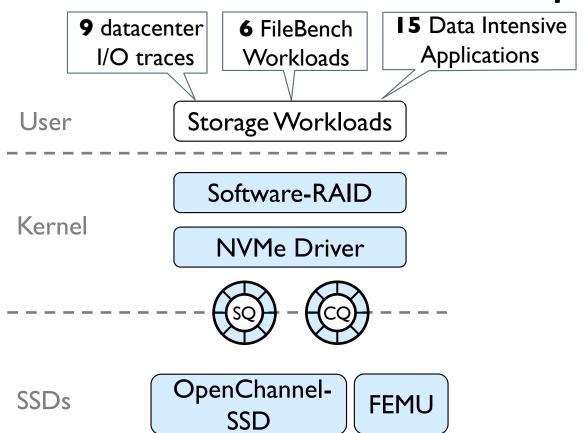

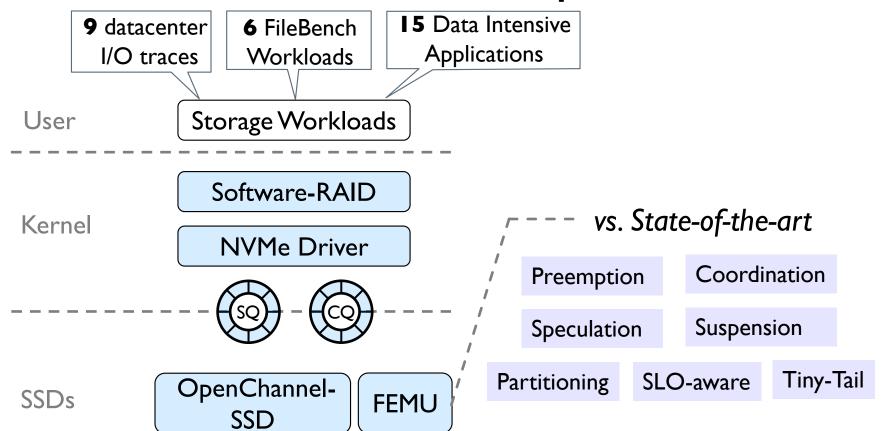

- □ Implementation

- Platforms: FEMU + OpenChannel-SSD

- Kernel: Linux Software-RAID + NVMe

- ☐ More evaluation results

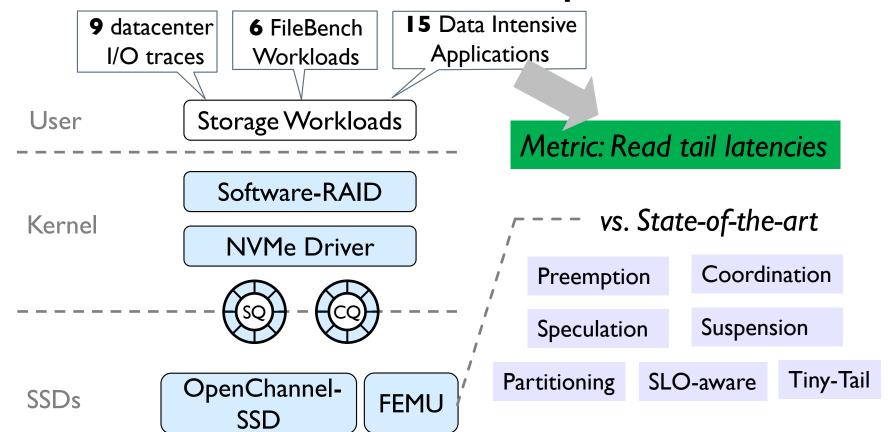

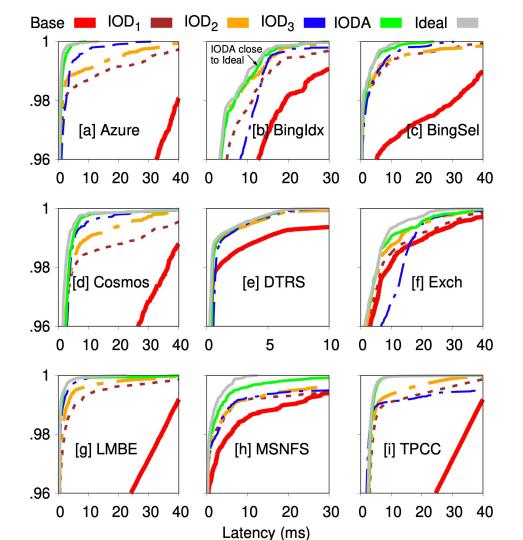

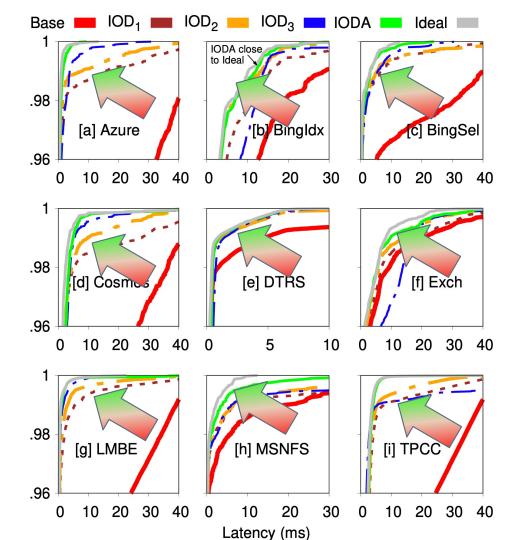

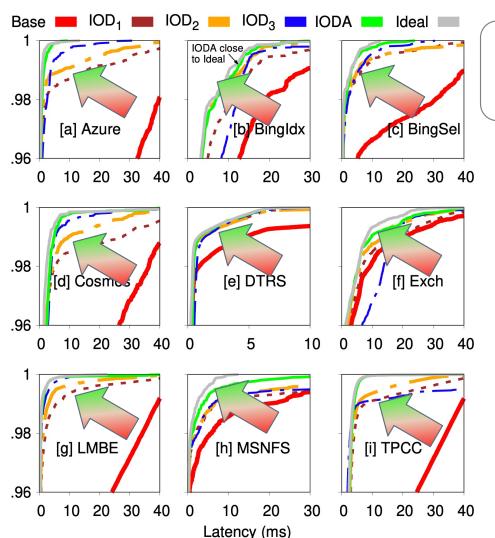

- 9 datacenter block traces + 21 real applications

- IODA vs. **7** State-of-the-art approaches

- IODA on OpenChannel-SSD

- IODA throughput and write latency

**-** ...

#### IODA: A Host/Device Co-Design for Strong Predictability Contract on Modern Flash Storage

Huaicheng Li University of Chicago and Carnegie Mellon University Martin L. Putra University of Chicago Ronald Shi University of Chicago

Xing Lin NetApp Gregory R. Ganger Carnegie Mellon University Haryadi S. Gunawi University of Chicago

#### Abstract

Predictable latency on flash storage is a long-pursuit goal, yet, supredictability story due to the unavoidable disturbance from many well-honow SSD internal activities. To combat this issue, the recent NYMe 10 Determinism (10D) interface advocates host-level controls to SSD internal management tasks. While promising, challenges remain on how to exploit

it for truly predictable performance. We present IODA, an I/O deterministic flash array design built on top of small but powerful extensions to the IOD interface for easy deployment. IODA exploits data redundancy in the context of IOD for a strong latency predictability contract In IODA, SSDs are expected to quickly fail an I/O on purpose to allow predictable I/Os through proactive data reconstruction. In the case of concurrent internal operations, IODA introduces busy remaining time exposure and predictable latency-window formulation to guarantee predictable data reconstructions. Overall. IODA only adds 5 new fields to the NVMe interface and a small modification in the flash firmware, while keeping most of the complexity in the host OS. Our evaluation shows that IODA improves the 95-99.99th latencies by up to 75x. IODA is also the nearest to the ideal. no disturbance case compared to 7 state-of-the-art preemp-tion, suspension, GC coordination, partitioning, tiny-tail flash

#### CCS Concepts

Computer systems organization → Firmware; Embedded hardware; Embedded software; Information systems

→ Flash memory; Hardware → Emerging interfaces.

controller, prediction, and proactive approaches.

Permission to make digital or but copies of all or part of this work for personal or classors as in granted witness for probled that copies are not made or distributed for prefit or consensual advantage and that copies been the notices and the full cutaint on the first page. Copping for correct of this work council by others than the authority many be boosted. Advantages with confid in permission. The copy of the contract problem is por one market to read interface the confidence of the contract problem in port and market to read any other than the contract problem. The contract protor read market to their copies agrees require for permission andreas for fineture of the contract problem. The contract problem is port on market 2002 T. 21. Cutates 7-29. 2021. Virtual Ericas Correspond

O 2021 Copyright held by the owner/author(s). Publication rights licensed to ACM. ACM ISBN 978-1-4503-8709-9/21/10... \$15.00

ACM ISBN 978-1-4503-8709-5/21/10...\$15.00 https://doi.org/10.1145/3477132.3483573

#### Keywords

Software/Hardware Co-Design, Predictable Latency, NVMe I/O Determinism, SSD, Flash Storage

#### ACM Reference Format:

Husicheng Li, Martin L. Putra, Ronald Shi, Xing Lin, Gregory R. Ganger, and Haryadi S. Gunawi. 2021. IODA: A HostDevice Co-Design for Strong Predictability Contract on Modern Flash Stonage. In ACM SIGOPS 28th Symposium on Operating Systems Principles (SOSP '21), October 26-29. 2021. Virtual Event, Germany: ACM, New York, NY, USA, 17 pages, https://doi.org/10.1145/34771523.3

#### 1 Introduction

Flash arrays are popular storage choices in data centers and they must address users' craving for low and predictable latencies [1-3]. Thus, many recent SSD products are released and evaluated not just on the average speed but the percentile latencies as well [4-7]. These all paint the reality that customers would like SSDs with deterministic latencies.

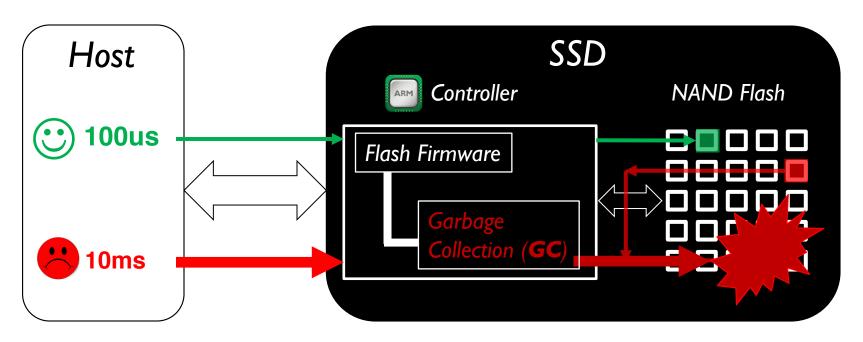

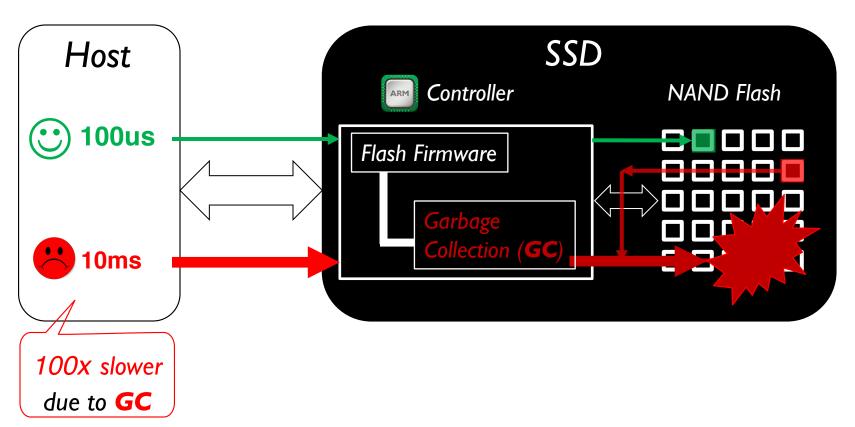

would like SAISW with a teremonate interies Deterministic latency, however, is hard to achieve because SSD performance is inherently non-deterministic due to the internal management activities such as the garbage collection (GC) = process, wear leveling, and internal buffer = flush [8–10]. These activities will in-

cviably trigger many background I/Os and disturb user resources. Noothly, GC is necessary path to recoreme NAND Flush's inshility for its place overwrites. It involves timeconsuming data movement to re-than upone and central with user requests, thereby causing severe latency background. As an intuitation, the right cost in the place thereby part factory, pay flush of the place of the place of the place of the place of the Modern SSDs often resort to large over provisioning space. SSDs showed that GCs of the place over provisioning space, que por S96 of designing experiments on center enterprise SSDs absword that GCs can still cause up to 60% latency in provide large of the place of the place of the place of the SSDs absword that GCs can still cause up to 60% latency in exposition of the place o

To tame the SSD performance challenges, there have been many efforts to evolve the device interfaces [15-17]. The Stor

SSDs OpenChannel-

#### **IODA** Evaluation

#### **IODA** Evaluation

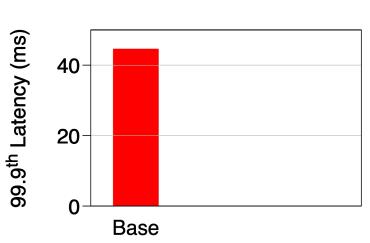

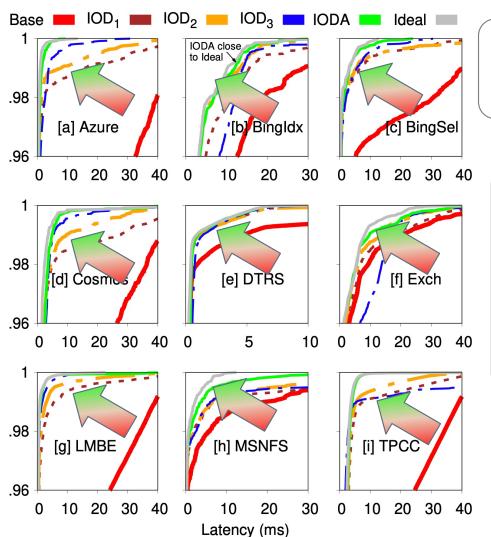

### **IODA** Results: (95th – 99.99th)

Up to 75x improvement over Base

# **IODA Results:** (95th – 99.99th) Up to 75x improvement over Base

VS. Coordination Preemption Suspension Speculation **SLO-aware** Tiny-Tail **Partitioning** IODA is more deterministic and efficient in cutting tail latencies!

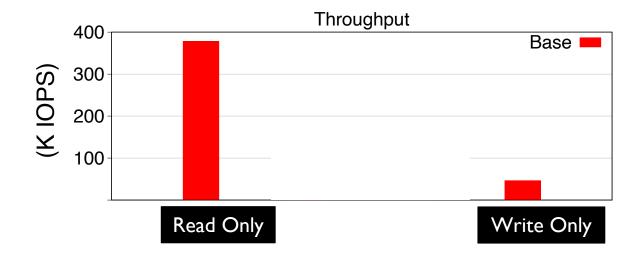

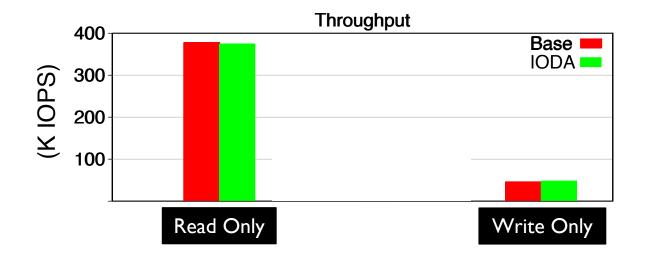

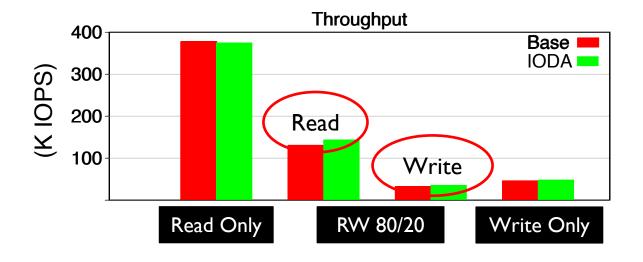

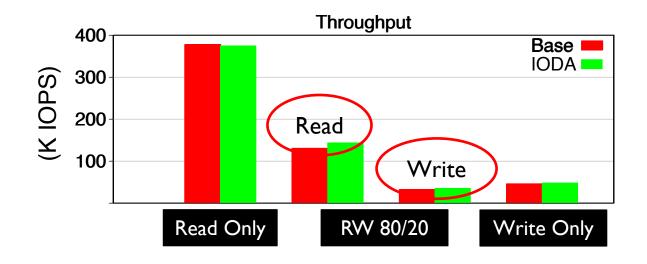

IODA doesn't sacrifice the array's aggregate bandwidth

### **IODA Takeaways**

- □ A Co-Design Approach for Performance Predictability

- Proactive reconstruction via fast-fail interface

- BRT for improved latencies

- TW formulation to program the window length

- Cross-device synchronization

I'm on the job market.

IODA: https://github.com/huaicheng/IODA

#### **IODA Takeaways**

- □ A Co-Design Approach for Performance Predictability

- Proactive reconstruction via fast-fail interface

- BRT for improved latencies

- TW formulation to program the window length

- Cross-device synchronization

## Thank you!

I'm on the job market.

IODA: https://github.com/huaicheng/IODA