#### THE UNIVERSITY OF CHICAGO

#### EVOLVING STORAGE STACK FOR PREDICTABILITY AND EFFICIENCY

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE

BY

HUAICHENG LI

CHICAGO, ILLINOIS

AUGUST 2020

COPYRIGHT © 2020 BY HUAICHENG LI

ALL RIGHTS RESERVED

Dedicated to my parents and significant other.

# TABLE OF CONTENTS

| Lis | st of F | igures . |                                                | <br>• | vii  |

|-----|---------|----------|------------------------------------------------|-------|------|

| Lis | st of T | ables .  |                                                | <br>• | xi   |

| Ac  | know    | ledgmen  | nts                                            |       | xiii |

| Ab  | stract  |          |                                                |       | xvi  |

| 1   | Intro   |          |                                                |       | 1    |

|     | 1.1     | Thesis   | Statement                                      |       | 2    |

|     | 1.2     | Perforn  | mance Predictability                           |       | 3    |

|     |         | 1.2.1    | Existing Approaches                            |       | 4    |

|     |         | 1.2.2    | Overview of Our Solutions                      |       | 7    |

|     | 1.3     | "Storag  | ge Tax" — Efficiency Challenge                 |       | 10   |

|     |         | 1.3.1    | LeapIO Introduction                            |       | 13   |

|     | 1.4     | Contrib  | butions                                        |       | 15   |

|     | 1.5     |          | Organization                                   |       | 16   |

| 2   | Back    | ground   | and Motivation                                 |       | 18   |

|     | 2.1     | _        | n Storage Stack Overview                       |       | 18   |

|     | 2.2     |          | e Primer                                       |       |      |

|     | 2.3     |          | rimer                                          |       | 22   |

|     | 2.4     |          | duced Tail Latency                             |       |      |

|     | 2.5     |          | atency in AFA                                  |       | 26   |

|     | 2.6     |          | Storage Deployment Goals                       |       | 28   |

| 3   | "Tail   | -free" F | Flash Storage Stack                            |       | 31   |

|     | 3.1     |          | OS: OS Support for Millisecond Tail Tolerance  |       |      |

|     |         | 3.1.1    | Deployment Model and Use Case                  |       |      |

|     |         | 3.1.2    | Use Case                                       |       |      |

|     |         | 3.1.3    | Goals / Principles                             |       |      |

|     |         | 3.1.4    | Design Challenges                              |       |      |

|     |         | 3.1.5    | Case Studies                                   |       |      |

|     |         | 3.1.6    | Disk Noop Scheduler (MITTNOOP)                 |       | 35   |

|     |         | 3.1.7    | SSD Management (MITTSSD)                       |       | 36   |

|     |         | 3.1.8    | A Sample Application: MongoDB                  |       | 38   |

|     | 3.2     |          | A: Tail-evading Flash Array for IO Determinism |       | 39   |

|     | ٥.2     | 3.2.1    | Fast-Fail and Busy Bits                        |       | 41   |

|     |         | 3.2.2    | Shortest BG Remaining Time                     |       | 42   |

|     |         | 3.2.2    | BG Time Window                                 |       | 43   |

|     |         | 3.2.3    | Time Window Algorithms                         |       | 45   |

|     |         | 3.2.4    | <u> </u>                                       |       | 43   |

|     |         | 5.4.5    | RAID size $(N_d)$                              | <br>• | 40   |

|   | 3.3 | TTFLASH: Tiny-Tail Flash Controller                                         | 50     |

|---|-----|-----------------------------------------------------------------------------|--------|

|   |     | 3.3.1 Plane-Blocking GC (PB)                                                | 51     |

|   |     | 3.3.2 RAIN                                                                  | 53     |

|   |     |                                                                             | 54     |

|   |     |                                                                             | 55     |

|   |     |                                                                             | 56     |

|   | 3.4 |                                                                             | 57     |

|   |     | 1                                                                           | 57     |

|   |     |                                                                             | 58     |

|   |     | 1                                                                           | 64     |

|   | 3.5 | 1                                                                           | 65     |

|   | 3.3 |                                                                             | 65     |

|   |     |                                                                             | 66     |

|   |     |                                                                             | 67     |

|   | 3.6 | •                                                                           | 68     |

|   | 3.0 |                                                                             |        |

|   |     | 11                                                                          | 69     |

|   |     | 11                                                                          | 71     |

|   |     | C 11                                                                        | 74     |

|   |     |                                                                             | 75<br> |

|   |     |                                                                             | 78     |

|   | 3.7 |                                                                             | 80     |

|   | 3.8 | Summary                                                                     | 81     |

| 1 | т   | -IO. Eff. dans and Danstalla Vinteral NIVIM - Channel and ADM Ca-Ca         | റ      |

| 4 | -   |                                                                             | 83     |

|   | 4.1 |                                                                             | 83     |

|   |     |                                                                             | 84     |

|   |     |                                                                             | 86     |

|   |     | ±                                                                           | 88     |

|   |     | 11 /                                                                        | 89     |

|   |     | Y 171                                                                       | 93     |

|   | 4.2 | Implementation                                                              |        |

|   |     | 4.2.1 NVMe over TCP and REST                                                | 95     |

|   |     | 4.2.2 Polling                                                               | 96     |

|   |     | 4.2.3 Virtual Interrupt                                                     | 97     |

|   | 4.3 | Evaluation                                                                  | 98     |

|   |     | 4.3.1 Software Overhead                                                     | 98     |

|   |     | 4.3.2 SoC Performance                                                       | 02     |

|   |     | 4.3.3 Composability                                                         | 04     |

|   | 4.4 | Summary                                                                     | 07     |

|   |     | -                                                                           |        |

| 5 | FEM | IU: Accurate, Scalable and Extensible NAND-Flash based NVMe SSD Emulator 10 | 08     |

|   | 5.1 | SSD Research Platform Introduction                                          | 08     |

|   | 5.2 | Extended Motivation                                                         | 11     |

|   |     | 5.2.1 The State of SSD Research Platforms:                                  | 1 1    |

|    |        | 5.2.2 The Lack of Large-Scale SSD Research    |

|----|--------|-----------------------------------------------|

|    |        | 5.2.3 The Rise of Software-Defined Flash      |

|    |        | 5.2.4 The Rise of Split-Level Architecture    |

|    |        | 5.2.5 The State of Existing Emulators         |

|    | 5.3    | FEMU Scalability                              |

|    |        | 5.3.1 QEMU I/O Scalabilty                     |

|    |        | 5.3.2 QEMU I/O Scalabilty Problem Root Causes |

|    |        | 5.3.3 Scalability Solutions                   |

|    |        | 5.3.4 FEMU Optimization Results               |

|    | 5.4    | FEMU Accuracy                                 |

|    |        | 5.4.1 Delay Emulation                         |

|    |        | 5.4.2 SSD Performance Models                  |

|    | 5.5    | FEMU Accurary Results                         |

|    |        | 5.5.1 Workloads & Experiment Setups           |

|    |        | 5.5.2 MicroBench Results                      |

|    |        | 5.5.3 MacroBench Results                      |

|    | 5.6    | FEMU Usability                                |

|    | 5.7    | FEMU Extensibility                            |

|    | 5.8    | Conclusion                                    |

|    |        |                                               |

| 6  |        | ussion                                        |

|    | 6.1    | MITTOS Limitations and Discussions            |

|    | 6.2    | TEAFA Discussions                             |

|    | 6.3    | TTFLASH Limitations and Discussions           |

|    |        | 6.3.1 TTFLASH Limitations                     |

|    | 6.4    | LeapIO Discussion                             |

|    |        | 6.4.1 Threat Model                            |

|    |        | 6.4.2 Cost Analysis                           |

|    |        | 6.4.3 ARM Offloading Capability               |

|    |        | 6.4.4 LeapIO Technical Novelties              |

|    |        | 6.4.5 Deployment                              |

| 7  | D -1   | 4. J.W. J.                                    |

| /  |        | ted Work                                      |

|    | 7.1    | Storage Performance                           |

|    | 7.2    | Storge Efficiency                             |

| 8  | Futu   | re Work                                       |

|    |        |                                               |

| 9  | Conc   | clusion                                       |

| R۵ | ferenc | 166                                           |

# LIST OF FIGURES

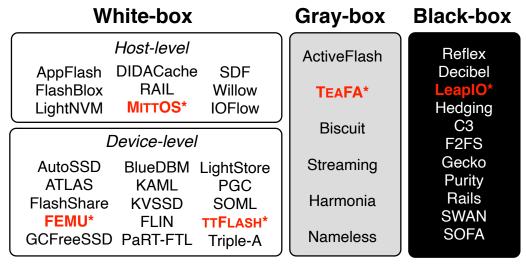

| 1.1 | Design space for achieving stable performance on top of modern Flash storage                                    |            |

|-----|-----------------------------------------------------------------------------------------------------------------|------------|

|     | stack. The figure depicts the design space of research in reducing tail latencies. The                          |            |

|     | x-axis represents the three spectrums, white-, gray-, and black-box approaches. Top left:                       |            |

|     | AppFlash [222], DIDACache [283], SDF [257], FlashBlox [170], RAIL [56], Willow [279],                           |            |

|     | LightNVM [126], MittOS [164], IOFlow [297]; Bottom left: AutoSSD [196], BlueDBM [183],                          |            |

|     | LightStore [137], ATLAS [149], KAML [178], PGC [220], FlashShare [328], KVSSD [190],                            |            |

|     | SOML [233], FEMU [228], FLIN [296], TTFLASH [318], GCFreeSSD [185], PaRT-FTL [249],                             |            |

|     | Triple-A [186]; Center: Nameless [330], Harmonia [209], Stream [207], Biscuit [155],                            |            |

|     | TEAFA [229], ActiveFlash [298]; Right: Reflex [211], Decibel [251], LeapIO [227], Hedg-                         |            |

|     | ing [105, 141], C3 [295], F2FS [218], Gecko [286], Purity [138], Rails [292], SWAN [201],                       |            |

|     | SOFA [134]                                                                                                      | 5          |

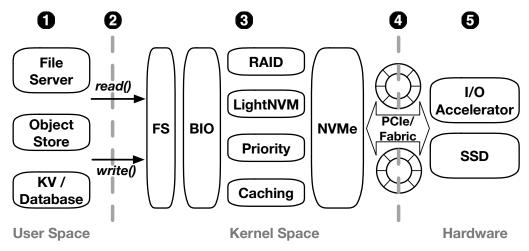

| 2.1 | Modern Storage Stack. The figure shows the simplified storage stack across storage                              |            |

| 2,1 | applications running at the user space, IO management functionalities (i.e., File/Block IO                      |            |

|     | stack) at the kernel space, storage/acceleration devices (e.g., SSDs and IO Accelerators) at                    |            |

|     | the hardware level, as well as the interfaces connecting them (i.e., POSIX sitting between user                 |            |

|     |                                                                                                                 | 19         |

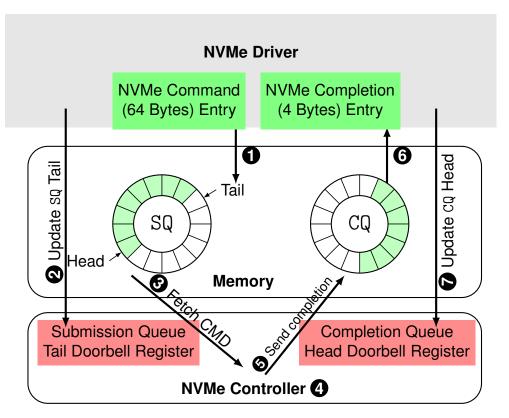

| 2.2 | <b>NVMe Architecture.</b> This figure presents the NVMe architecture, including the inter-                      | 17         |

| 2,2 | action between the host-side NVMe driver and the device-side NVMe device controller                             |            |

|     | (e.g., FEMU, LeapIO, TEAFA). SQ and CQ represent the submission and completion                                  |            |

|     | queues. The I/O processing logic is denoted as $(1)$ to $(7)$ , with a detailed explanation                     |            |

|     |                                                                                                                 | 21         |

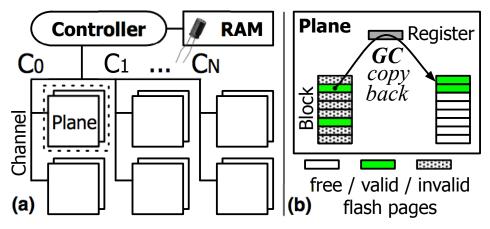

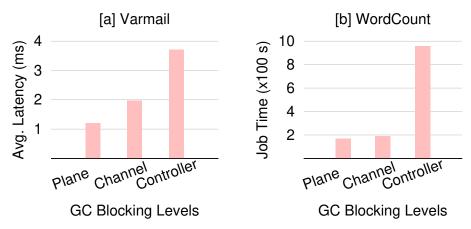

| 2.3 |                                                                                                                 | 21<br>23   |

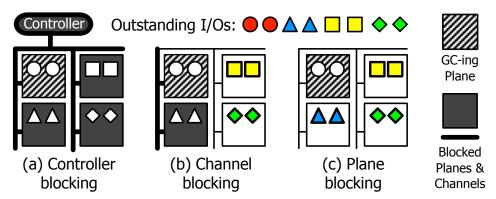

| 2.3 | Various levels of GC blocking. Colored I/Os in bright planes are servable while non-                            | <i>د</i> 2 |

| 2.4 | colored I/Os in dark planes are blocked. (a) In controller-blocking (§2.3), a GC blocks the                     |            |

|     | controller/entire SSD. (b) In channel-blocking (§2.3), a GC blocks the channel connected to                     |            |

|     |                                                                                                                 | 24         |

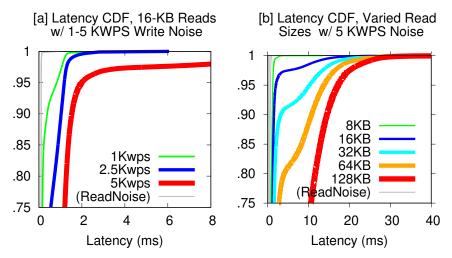

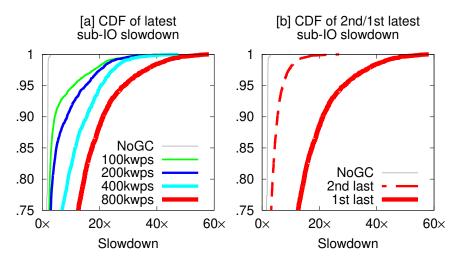

| 2.5 |                                                                                                                 | 24<br>26   |

| 2.6 | DCSSD GC Impacts in SSD Array (Section 2.5). Each experiment runs on a RAID-0                                   | 20         |

| 2.0 |                                                                                                                 | 27         |

| 27  |                                                                                                                 | 21<br>29   |

| 2.7 | Goals. As described in Section 2.6                                                                              | 29         |

| 3.1 | * · · · · · · · · · · · · · · · · · · ·                                                                         | 32         |

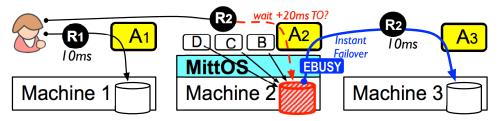

| 3.2 | ,                                                                                                               | 34         |

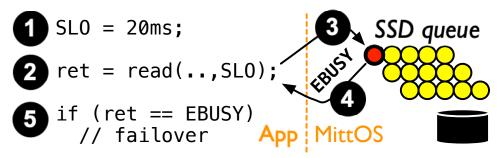

| 3.3 | TTFLASH Architecture. The figure illustrates our RAIN layout (§3.3.2), GC-tolerant read                         |            |

|     | $(\S 3.3.3)$ , rotating GC $(\S 3.3.4)$ , and GC-tolerant flush $(\S 3.3.5)$ . We use four channels $(C_0-C_3)$ |            |

|     | for simplicity of illustration. Planes at the same "vertical" position form a plane group $(G_0,$               |            |

|     | 1 11 0 1 0 1                                                                                                    | 53         |

| 3.4 |                                                                                                                 | 66         |

| 3.5 |                                                                                                                 | 66         |

| 3.6 | <b>Prediction inccuracy.</b> (As explained in §3.5.3)                                                           | 67         |

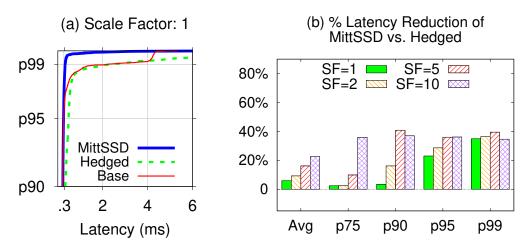

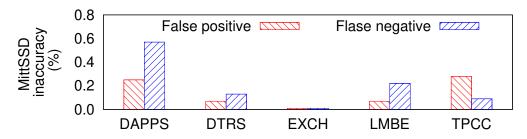

| 3.7   | <b>TEAFA</b> percentile latencies and #busy sub-IOs with TPCC (§3.6.1). Figure (a)                                                                                    |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | shows the TPCC read latencies (in y-axis) at major percentiles p75 to p99.99 (in x-axis) with                                                                         |    |

|       | various TEAFA strategies (Tea1, Tea2, and TeaFA) compared to the Base line and the ideal                                                                              |    |

|       | NoGC case. Figure (b) shows the percentage of stripe-level reads (in y-axis) that experience 1                                                                        |    |

|       | to 4 busy sub-IOs (in x-axis). It shows that TEAFA converts multiple concurrent busy sub-IOs                                                                          |    |

|       | to at most one busy sub-IO per stripe in RAID-5, thus always guaranteeing reconstructability                                                                          |    |

|       | of busy reads                                                                                                                                                         | 70 |

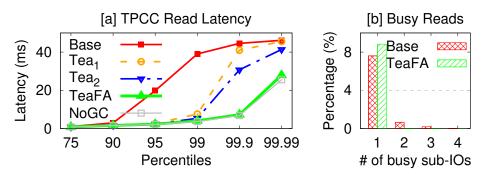

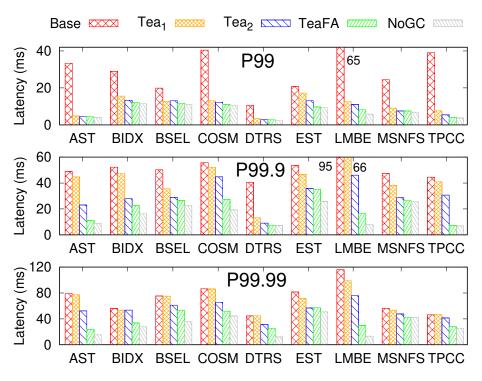

| 3.8   | TEAFA p99, p99.9, and p99.99 latencies with all the workloads (§3.6.2). The                                                                                           |    |

|       | figures show the p99 (top figure), p99.9 (center) and p99.99 (bottom) latencies of all the work-                                                                      |    |

|       | loads under different TEAFA strategies including the Base and NoGC cases. It shows that                                                                               |    |

|       | TEAFA successfully evades tail latencies and almost reaches the NoGC values at high per-                                                                              |    |

|       | centiles                                                                                                                                                              | 72 |

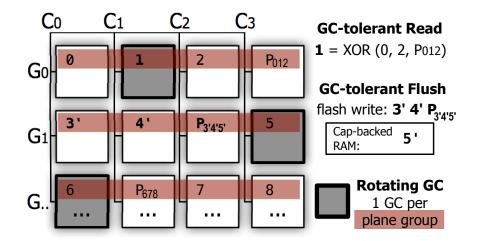

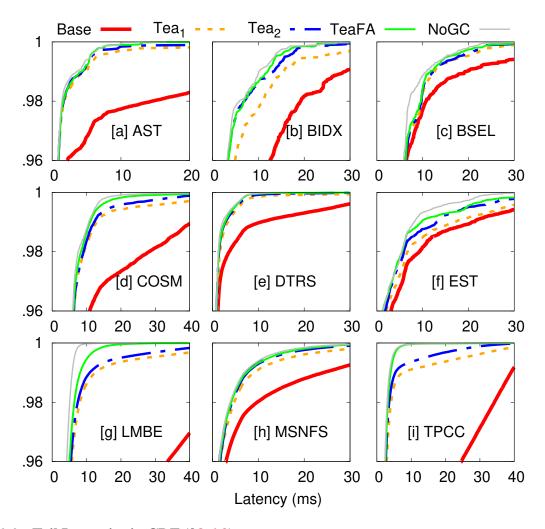

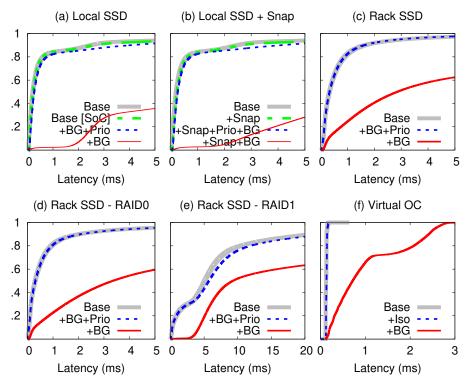

| 3.9   | <b>Tail Latencies in CDF</b> (§3.6.2). <i>The figures represent the same experiments in Figure 3.8.</i>                                                               |    |

|       | The figures basically show a more complete picture (in CDF above p96) of the p99 and p99.9                                                                            |    |

|       | values shown in Figure 3.8.                                                                                                                                           | 74 |

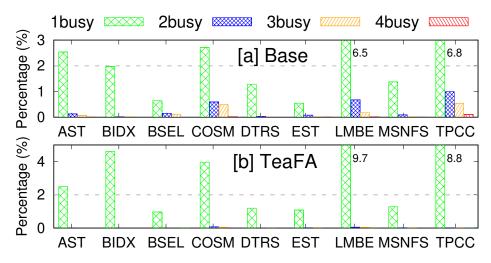

| 3.10  | , , , , , , , , , , , , , , , , , , , ,                                                                                                                               |    |

|       | figure in Figure 3.7b (that only shows TPCC), but now we show the results from all workloads.                                                                         |    |

|       | The 1busy to 4busy bars represent the number of busy sub-IOs per stripe, and the y-axis shows                                                                         |    |

|       | the percentage of stripe-level reads that experience busy sub-IOs. The bottom figure essentially                                                                      |    |

| 2.11  | shows that TEAFA successfully shifts multiple concurrent 2-4busy sub-IOs to 1busy sub-IOs.                                                                            | 75 |

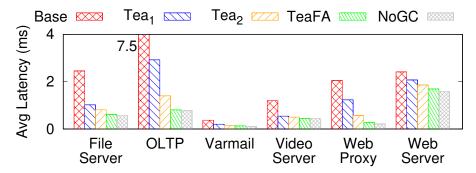

| 3.11  |                                                                                                                                                                       |    |

|       | experiments by running 6 different storage workloads using Filebench on top of ext4 file system.                                                                      | 7  |

| 2.12  | We report the average read latencies as Filebench doesn't support per-IO latency tracking.                                                                            | 76 |

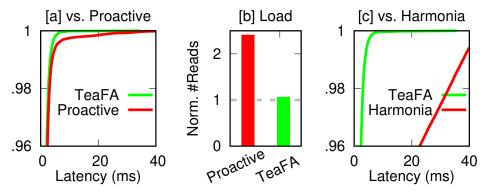

| 3.12  | vs. Proactive and Harmonia (§3.6.4-3.6.4). Figure (a) compares the TPCC CDF laten-                                                                                    |    |

|       | cies on TEAFA vs. Proactive. Figure (b) shows the normalized number of IOs that Proactive                                                                             |    |

|       | and TEAFA send down to the flash array (2.4× vs. 6%). Figure (c) compares the TPCC                                                                                    | 7/ |

| 2 12  | latencies on TEAFA vs. Harmonia.                                                                                                                                      | 76 |

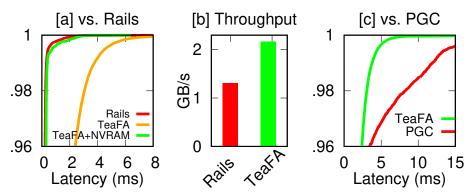

| 3.13  | vs. Rails and Preemptive GC (§3.6.4-3.6.4). Figure (a) shows the TPCC read CDF                                                                                        |    |

|       | latencies on TEAFA vs. Rails. Figure (b) shows user-perceived read throughput on Rail vs.  TEAFA. Figure (c) shows the TPCC read latencies on TEAFA vs. Preemptive GC | 77 |

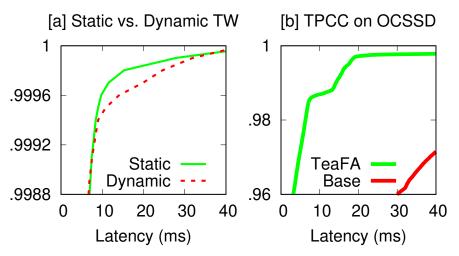

| 3 1/1 | Extended evaluations on Dynamic time window. Dynamic Time Windows                                                                                                     | 79 |

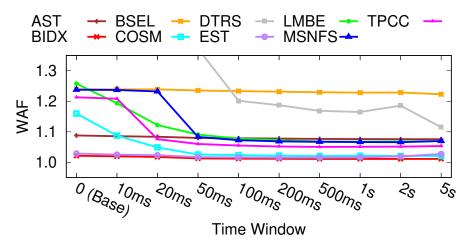

|       | Time window impacts to write amplification (§3.6.5). The figure shows the resulting                                                                                   | 15 |

| 3.13  | write amplification factor (WAF) in the y-axis when different static time window values are                                                                           |    |

|       | used (in the x-axis) for a variety of workloads                                                                                                                       | 80 |

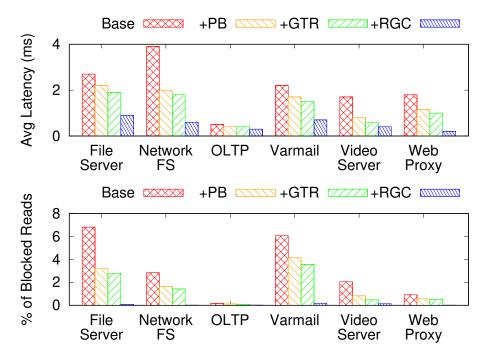

| 3 16  | <b>Filebench on</b> ttFlash-Emu. The top and bottom figures show the average latencies of                                                                             | 00 |

| 5.10  | read operations and the percentage of GC-blocked reads, respectively, across six filebench                                                                            |    |

|       | personalities. "Base" represents our VSSIM++ with channel-blocking (§3.4)                                                                                             | 81 |

|       | personantes. Bass represents our rooms in min channel brooming (35.1).                                                                                                | 01 |

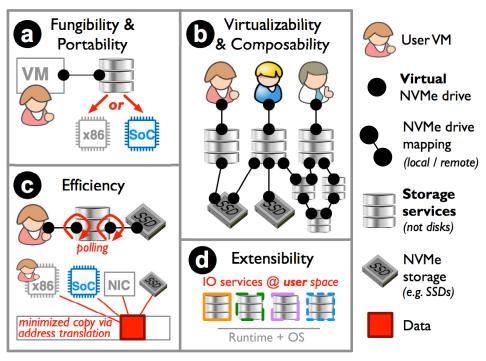

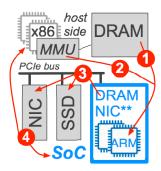

| 4.1   | <b>Hardware requirements.</b> The figure is explained in Section 4.1.1. "NIC**" means an                                                                              |    |

|       | optional feature of the SoC. $x \rightarrow y$ means x should be exposed or accessible to y                                                                           | 85 |

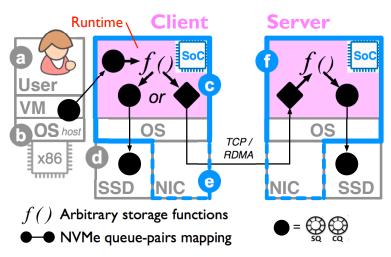

| 4.2  | <b>Software view.</b> The figure shows the software design of LeapIO (Section 4.1.2). For sim-         |     |

|------|--------------------------------------------------------------------------------------------------------|-----|

|      | plicity, we use two nodes, client and server, running in a datacenter. The arrows in the figure        |     |

|      | only represent the logical control path, while the data path is covered in §4.1.4. Our runtime         |     |

|      | and storage services (the shaded/pink area) can transparently run in the SoC (as shown above)          |     |

|      | or on the host x86 via our "SoC <sub>VM</sub> " support (in §4.1.5)                                    | 87  |

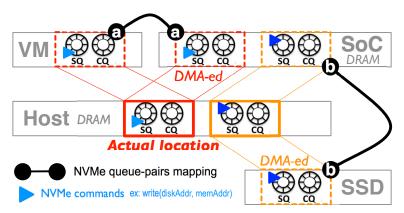

| 4.3  | <b>Control setup.</b> The figure shows the mappings of NVMe queue pairs to pass IO commands            |     |

|      | across the hardware and software components in LeapIO, as described in §4.1.3                          | 88  |

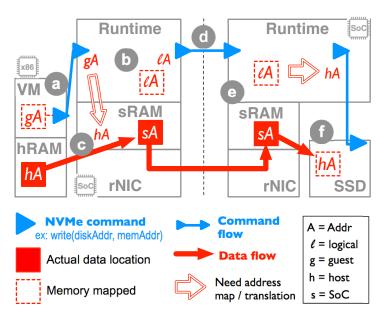

| 4.4  | <b>Datapath and address translation.</b> The figure shows how we achieve an efficient data             |     |

|      | path (minimized copy) with our address translation support, as elaborated in §4.1.4. The figure        |     |

|      | only shows write path via RDMA (read path is similar)                                                  | 91  |

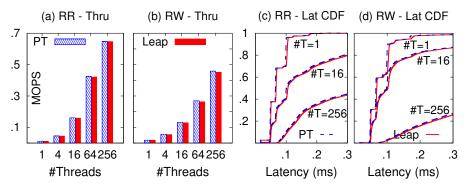

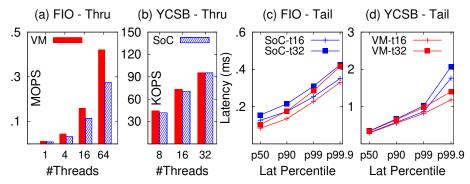

| 4.5  | <b>LeapIO vs. Pass-through (PT) with FIO.</b> The figure compares LeapIO and PT per-                   |     |

|      | formance as described in §4.3.1(1). From left to right, the figures show read-only (RR) and            |     |

|      | read-write (RW) throughputs followed with latency CDFs                                                 | 99  |

| 4.6  | <b>Leap vs. PT (YCSB/RocksDB).</b> The figure compares LeapIO and pass-through (PT) as                 |     |

|      | described in §4.3.1(2)                                                                                 | 100 |

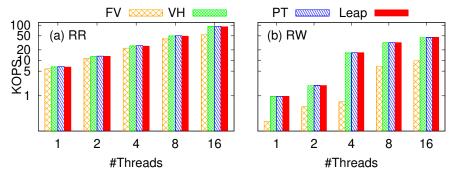

| 4.7  | Leap vs. other virt. technologies. The figure compares LeapIO with full virtualization                 | 100 |

| ,    | (FV) and virtual host (VH) as described in §4.3.1(3)                                                   | 100 |

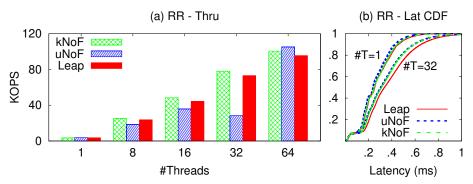

| 4.8  | <b>LeapIO vs. kernel/user NVMeoF.</b> We compare LeapIO remote NVMe feature with kernel                | 100 |

|      | and user NVMeoF (KNOF and UNOF). UNOF is unstable; with 32 threads, at p99.9 UNOF                      |     |

|      | reaches 14ms while LeapIO can deliver 1.4ms, and at p99.99 UNOF reaches almost 2000ms                  |     |

|      | while LeapIO is still around 7ms.                                                                      | 101 |

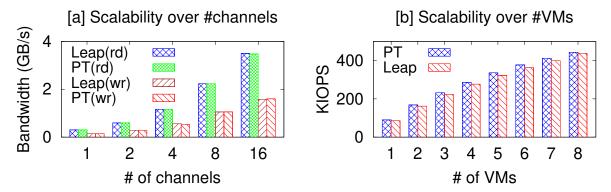

| 4.9  | <b>Scalability experiment results.</b> <i>The figure is explained in Section §3.5.</i>                 |     |

| 4.10 | • •                                                                                                    | 102 |

| 0    | (local and remote) running on a SoC vs. in a SoC <sub>VM</sub> as described in §4.3.2                  | 103 |

| 4.11 |                                                                                                        | 105 |

|      | $SoC_{VM}$ for faster evaluation. In (a), we run one experiment on $SoC$ "[ $SoC$ ]" to show a similar |     |

|      | •                                                                                                      | 105 |

|      | ршет                                                                                                   | 103 |

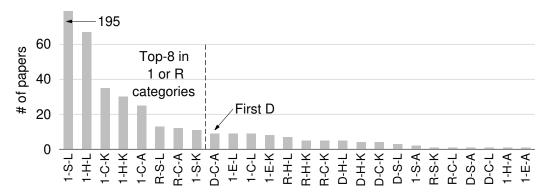

| 5.1  | Categorization of SSD research. The figure is explained in Section §5.2. The first bar                 |     |

|      | reaches 195 papers                                                                                     | 111 |

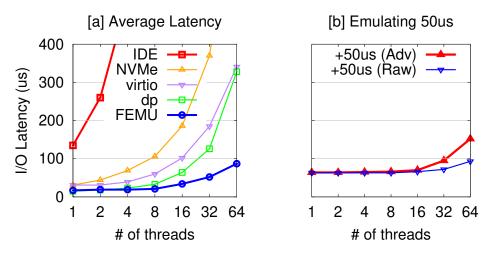

| 5.2  | <b>QEMU Scalability.</b> The figure shows the scalability of QEMU's IDE, NVMe, virtio, and             |     |

|      | dataplane (dp) interface implementations, as well as FEMU. The x-axis represents the number            |     |

|      | of concurrent IO threads running at the user level. Each thread performs random 4KB read               |     |

|      | IOs. The y-axis shows the user-perceived average IO latency. The storage is memory-backed,             |     |

|      | thus the IO latency represents the software overhead. The experiments were run on a dual-              |     |

|      | thread (2x) 24-core machine, hence no CPU contention. For Figure (a), the IDE and NVMe                 |     |

|      | lines representing VSSIM and LightNVM's QEMU respectively are discussed in §5.2; virtio,               |     |

|      | dp, and FEMU lines in §5.3. For Figure (b), the "+50 $\mu$ s (Raw)" line is discussed in §5.4.1;       |     |

|      | the " $+50\mu s$ (Adv)" line in "Result 3" part of §5.4.2                                              | 117 |

|      |                                                                                                        |     |

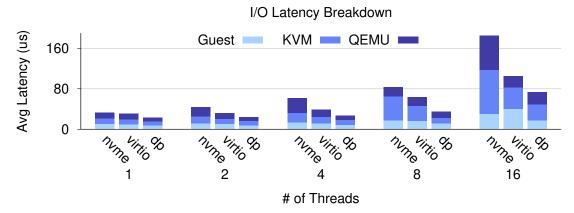

| 5.3        | QEMU latency breakdown under NVMe, virtio-blk (virtio) and virtio-dataplane                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | (dp). This figures show the latencies brought by each parts in I/O life cycle. It helps us analyze                                                                    |

|            | the scalability of each part. "Guest OS" accounts for the time since the IO enters guest kernel                                                                       |

|            | until driver I/O submission, "KVM" represents the time taken for I/O virtualization handling                                                                          |

|            | in the host kernel plus QEMU post processing before entering corresponding device emulation                                                                           |

|            | layer, and "QEMU" shows the time of I/O processing in QEMU I/O emulation                                                                                              |

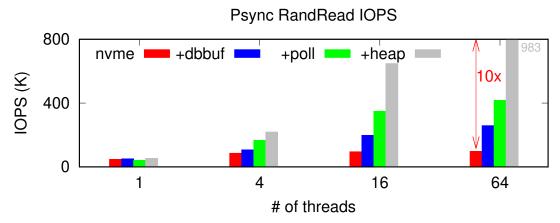

| 5.4        | QEMU NVMe IOPS w/ FEMU optimizations. The figure shows the scalability of                                                                                             |

|            | QEMU's NVMe implementation under our optimizations. nume line represents stock QEMU                                                                                   |

|            | NVMe, +dbbuf represents QEMU NVMe with shadow doorbell buffer support, +poll adds                                                                                     |

|            | polling based on +dbbuf, and finally +heap applies our own heap storage backend on top of                                                                             |

|            | all previous optimizations. The x-axis represents the number of concurrent IO threads running                                                                         |

|            | at the user level. Each thread performs random 4KB read IOs. The y-axis shows aggregate                                                                               |

|            | <i>IOPS achieved.</i>                                                                                                                                                 |

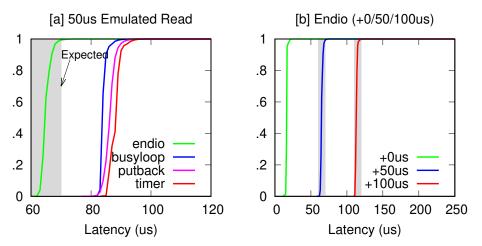

| 5.5        | <b>Delay Emulation:</b> 50 $\mu$ s and 100 $\mu$ s. <i>Emulating</i> 50 $\mu$ s and 100 $\mu$ s device access latency,                                                |

|            | FEMU delay emulation doesn't introduce tail latencies                                                                                                                 |

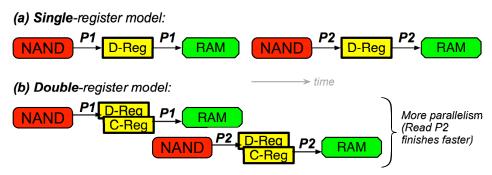

| 5.6        | <b>Single- vs. double-register model.</b> (a) In a single-register model, a plane only has one                                                                        |

|            | data register (D-Reg). Read of page P2 cannot start until P1 finishes using the register (i.e.,                                                                       |

|            | the transfer to the controller's RAM completes). (b) In a double-register model, after P1 is                                                                          |

|            | read to the data register, it is copied quickly to the cache register (D-Reg to C-Reg). As the                                                                        |

|            | data register is free, read of P2 can begin (in parallel with P1's transfer to the RAM), hence                                                                        |

|            | finishes faster                                                                                                                                                       |

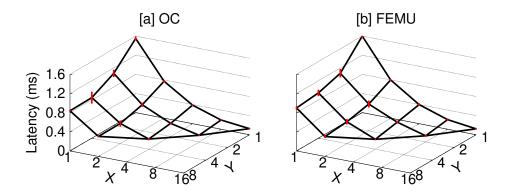

| 5.7        | <b>OpenChannel SSD (OC) vs. FEMU.</b> X: # of channels, Y: # of planes per channel. The                                                                               |

|            | figures are described in §5.5.2. The red line represents latency standard errors. For each                                                                            |

|            | configuration set (X, Y), we run the same fio workloads on both FEMU and OC and collect                                                                               |

|            | latency numbers. This experiment is to show FEMU can accurately emulate the queueing                                                                                  |

|            | delay when multiple I/Os are sent to one NAND chip and parallelism when multiple I/Os are                                                                             |

| <b>5</b> 0 | served evenly by multiple NAND chips                                                                                                                                  |

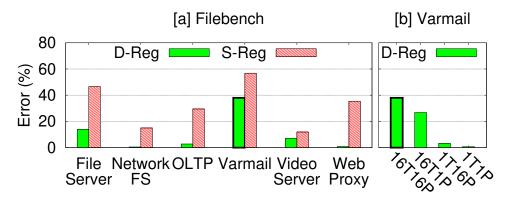

| 5.8        | Filebench on OpenChannel SSD (OC) vs. FEMU. The figures are described in the                                                                                          |

|            | "Result 2" segment of §5.5.3. The y-axis shows the latency difference (error) of the benchmark                                                                        |

|            | results on OC vs. FEMU (Error=(Lat <sub>femu</sub> -Lat <sub>oc</sub> )/Lat <sub>oc</sub> ). D-Reg and S-Reg represent the                                            |

|            | advanced and basic model respectively. The two bars with bold edge in Figures (a) and (b) are                                                                         |

| 5.0        | the same experiment and configuration (varmail with 16 threads on 16 planes)                                                                                          |

| 5.9        | Use examples. Figure 5.9a is described in the "FTL and GC schemes" segment of Section  5.6 Figure 5.0b is discussed in the "Distributed SSDs" assured of Section 5.6. |

|            | 5.6. Figure 5.9b is discussed in the "Distributed SSDs" segment of Section 5.6                                                                                        |

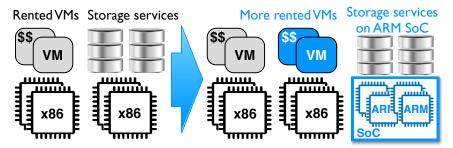

| 6.1        | <b>LeapIO Goal.</b> By offloading storage services to ARM SoCs, we release more host CPU                                                                              |

|            | resources for rented VMs                                                                                                                                              |

# LIST OF TABLES

| <b>Real storage functions, not offload ready.</b> The table summarizes why real cloud drive services are either not completely offload ready or not easily composable with each other                                                                                                                                                                                                                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Symbols</b> (§3.2.4). The table explains the symbols used in TEAFA's WINDOW algorithm. The top part are the basic properties of modern datacenter SSDs [77, 126] and the bottom part are the derived values. The right-most column shows example values we use in Section 3.2.4                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>SSD Parameters.</b> This paper uses the above parameters. (**) 1 planes/chip is for simplicity of presentation and illustration. The latencies are based on average values; actual latencies can vary due to read retry different voltages, etc. Flash reads/writes must use the plane register.                                                                                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Block trace charateristics. This table show the detailed characteristics of the blocks traces we use. "#IOs" represents the total number of IOs in the trace, "Read%" means the percentage of reads in each trace, and "Read size, Write size, IO Max" represents the average read, write and max IO size. "Inter-time" means the average inter-arrival time between two consecutive IOs in each trace                                             | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LeapIO complexity (LOC). (As described in §3.4)                                                                                                                                                                                                                                                                                                                                                                                                    | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SSD Research Platforms Comparison. SSD Research Platform Pros & Cons: Simulator                                                                                                                                                                                                                                                                                                                                                                    | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FEMU emulated OpenChannel-SSD Parameters. We use the above parameters for the emulated SSD. Latency numbers are profiled from a real enterprise OpenChannel-SSD. The latencies are based on average values; actual latencies can vary due to read retry, different voltages, etc. Flash reads/writes must use the plane register. We use 128 GB out of 256 GB physical memory to serve as the emulated SSD backend storage. For the microbenchmark | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| experiments, we change #Channels & #Planes/channel combinations to verify the latency ac-                                                                                                                                                                                                                                                                                                                                                          | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| experiments, we change #Channels & #Planes/channel combinations to verify the latency accuracy under different settings                                                                                                                                                                                                                                                                                                                            | 131<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbols (§3.2.4). The table explains the symbols used in TEAFA's WINDOW algorithm. The top part are the basic properties of modern datacenter SSDs [77, 126] and the bottom part are the derived values. The right-most column shows example values we use in Section 3.2.4 SSD Parameters. This paper uses the above parameters. (**) I planes/chip is for simplicity of presentation and illustration. The latencies are based on average values; actual latencies can vary due to read retry, different voltages, etc. Flash reads/writes must use the plane register.  Block trace charateristics. This table show the detailed characteristics of the blocks traces we use. "#IOs" represents the total number of IOs in the trace, "Read%" means the percentage of reads in each trace, and "Read size, Write size, IO Max" represents the average read, write and max IO size. "Inter-time" means the average inter-arrival time between two consecutive IOs in each trace  LeapIO complexity (LOC). (As described in §3.4)  SSD Research Platforms Comparison. SSD Research Platform Pros & Cons: Simulator v.s. Emulator v.s. Hardware platforms  Emulated OpenChannel-SSD Parameters. We use the above parameters for the emulated SSD. Latency numbers are profiled from a real enterprise OpenChannel-SSD. The latencies are based on average values; actual latencies can vary due to read retry, different voltages, etc. Flash reads/writes must use the plane register. We use 128 GB out of 256 |

#### ACKNOWLEDGMENTS

It is with tremendous help and support from many people that this Ph.D. is made possible and unique. I am very grateful to these individuals and would like to thank them in this special section.

First and foremost, I am deeply indebted to my advisor, Haryadi Gunawi, for his tireless mentoring, guidance, and assistance during my Ph.D. study. Haryadi was not my assigned advisor when I first came to University of Chicago. But my passion in Operating/Storage Systems research urged me to talk to him soon after I arrived in Chicago. Haryadi saw my passion and kindly took me into his group. Until today, I still feel lucky our first conversation worked out and it earned me the opportunity for me to pursue my research dreams in Systems!

Haryadi provided me all the necessary help to grow into a successful researcher. He always puts his students in the first place. Thus, I have never found it difficult to reach him, either through Skype/Email or office visits. Besides our weekly meetings, my sporadic visits to his office significantly boosted my research progress during the first two years in timely clearing potential miscommunications and getting quick feedback on intermediate results. Haryadi knows us very well and he customizes the advising styles to best suit each student. I benefited a lot from this style in reflecting and overcoming my shortcomings as well as building my advantage. Given my interest in developing a research career in academia, Haryadi gave me first-hand experience of the professional lifestyle and helped me develop my own style in effectively advising students and broadening my network by attending conferences, reviewing papers, and mentoring students. As for research, Haryadi always holds high standards and pushes me to think one level deeper. From him, I learned to make short-term "visible" progress by thinking ahead to divide the tasks into small pieces. I believe this will become a fundamental rule I will stick to for my future research. Haryadi is a role model to me with many good qualities: He is diligent, and I run into him many times in the hallway during weekends at both Ryerson and JCL; He is organized, and my Ph.D. life becomes much easier thanks to many automation scripts he shared; He is caring, and I'm grateful to his help in paper revising, internship recommendations, and allowing me the freedom to pursue what interests me most.

I would like to thank Andrew Chien and Anirudh Badam for helping serve on my committee and their feedback on my dissertation makes it much stronger. Andrew has been a long-time collaborator and I always learn a lot from his wisdom through conversations and lectures. Anirudh is a mentor as well as a friend to me. I was lucky enough to be his intern in 2018 at Microsoft Research and he greatly influenced my research mindset. Moreover, I'm also grateful for their support during my job search.

Additionally, many thanks to the UCARE members (alphabetical order) for the friendship and for making the UCARE group a warm hub for mutual encouragement and fun: Cesar Stuardo, Daniar Kurniawan, Huan Ke, Jeffery Lukman, Michael Hao Tong, Mingzhe Hao, Meng Wang, Riza Suminto, Shiqin Yan, Tanakorn Leesatapornwongsa.

I'm fortunate to have mentored several outstanding undergraduate and master students: Martin L. Putra, Fadhil I. Kurnia, Ronald Shi, Yesa Rahmad, etc.. Thank you for your contributions to the research projects!

The life at University of Chicago wouldn't be so joyful without many friends. Thank you, Dixin Tang, Guangpu Li, Shu Wang, Yi Ding, Yun Li, Yuxi Chen, Zechao Shang and Zhixuan Zhou for the many dinners/conversations we shared and the fun we had together.

I also want to thank the CERES research center, the CS department, and our awesome staff. The CERES summits have been an excellent opportunity for me to socialize with others and learn about many interesting ongoing works. I feel lucky to grow together with the department in the last five years. And the tech and admin staff are very nice. I want to thank them for their services: Bob Bartlett, Colin Hudler, Donna Brooms, Margaret P. Jaffey, Nita K. Yack, Phil Kauffman, and Tom Dobes. In particular, I frequently bug Bob, Tom, and Phil for hardware purchases, fixing networking issues, and setting up special hardware, and I'm really grateful that they kindly help guide me through these.

There are many other collaborators, mentors, and friends I enjoyed working with and I would

like to express my gratitude to. I have been very fortunate to be a 3× research intern at Microsoft Research throughout my Ph.D., working with many smart people: Dan R. Ports, Daniel S. Berger, Irene Zhang, Jaeyoung Do, Ricardo Bianchini, and Stanko Novakovic. I enjoyed many insightful discussions with them. I also spent a few months at NetApp ATG working with Xing Lin, Fan Ni, and Art Harkin. Many thanks to them for kindly hosting me during an irregular period of time. Matias Bjørling and Javier Gonzalez helped me a lot when I started working on OpenChannel-SSDs, and I appreciate that!

Lastly, I want to express my gratitude to my family for their unconditional love. My parents work very hard to support the entire family and provide me the best they can. Their perseverance and diligence always motivate me to aim higher and better and never stop moving forward. My significant other, Jingyu Zhang, and I have been together for 8 years and I couldn't thank her more for her company and the happy time we spent together along the way. She lightened the spark in me to pursue a Ph.D. and encouraged me to come to the U.S. for graduate school even though we would be separated by the Pacific Ocean. I dedicate this dissertation to her and my parents.

#### **ABSTRACT**

With the exponential growth of data that are expected to reach 175 zettabytes by 2025, cloud storage is increasingly becoming the central hub for data management and processing. Among the many benefits cloud platforms promise, predictable performance and cost-efficiency are two fundamental factors driving the success of modern cloud storage. However, under rapid changes in modern cloud storage infrastructure in terms of both software and hardware, new challenges emerge for achieving predictable performance with efficiency.

In more detail, modern data intensive applications and the new wave of computing paradigms (e.g., data analytics, ML, serverless) drive the storage stack to undergo a radical shift towards more feature-rich software designs on top of increasingly heterogeneous architectures. As a result, today's cloud storage stack is extremely heavy-weight and complex, burning 10-20% of data center CPU cycles and introducing severe performance non-determinism (i.e., long tail latencies). Unfortunately, the deployment of new acceleration hardware (e.g., NVMe SSDs and IO co-processors) only partially addresses the problem. Due to the intrinsic complexities and idiosyncrasies in hardware (e.g., NAND Flash management) and lack of system-level support, it remains a challenge to design performant and cost-efficient cloud storage systems. In particular, achieving sub-millisecond level latency predictability in a cost-efficient manner is the new battlefield.

Rooted in deep understanding and analysis of existing software/hardware stack, this dissertation focuses on building new abstractions, interfaces, and end-to-end storage systems to achieve predictable performance and cost-efficiency using a software/hardware co-design approach. By revisiting the challenges across different layers in a holistic manner, the co-design approach opens up simple yet powerful system-level policy designs to opportunistically exploit hardware idiosyncrasies and heterogeneity. The systems we build can effectively decrease latency spikes by up to orders of magnitude and increase cost savings by  $20\times$ .

To address the challenge of predictable performance in modern Flash storage systems, we present TEAFA, a tail-evading flash array design delivering deterministic performance. TEAFA

uniquely combines a simple yet powerful host-SSD interface, time window mechanism, and data redundancy to proactively and deterministically reconstruct late requests, with only minor changes to the host software and device firmware. The evaluation results across 9 data center storage traces and several real storage workloads (*e.g.*, FileBench, YCSB/RocksDB) show that TEAFA improves the baseline by orders of magnitude and is only  $1.1 \times$  to  $2.1 \times$  slower than an ideal case where there are no background operations induced tail latencies. When compared to other state-of-the-art works (*e.g.*, Proactive approach, Preemptive GC, P/E Suspension, Flash-on-Rails, and Harmonia) focusing on improving IO performance, TEAFA is more deterministic and effective in cutting tail latencies while being less intrusive and easy to deploy. Along with TEAFA, we also introduce OS-level and device-level approaches, MITTOS and TTFLASH, respectively, to eliminate tail latencies across the entire storage stack.

Although TEAFA can effectively improves tail latencies, a significant portion of CPU cycles is needed to fulfill the reconstruction computations. Worse, at a large scale, the "storage tax" that cloud providers have to pay takes up to 10-20% of datacenter CPU cycles. Thus, it's challenging to achieve cost/resource-efficiency in modern cloud storage stack designs. One opportunity is to utilize modern IO accelerators for cost-efficient storage offloading. Yet, the complex cloud storage stack is not completely offload-ready to today's IO accelerators. To tackle the cost-efficiency challenge, we present LeapIO, a next-generation cloud storage stack that leverages ARM-based coprocessors to offload complex storage services. LeapIO addresses many deployment challenges, such as hardware fungibility, software portability, virtualizability, composability, and efficiency. It employs a set of OS/software techniques and new hardware properties to provide a uniform address space across the x86 and ARM cores to minimize data copies and directly expose virtual NVMe storage to unmodified guest VMs. At the core, LeapIO runtime enables agile storage service development at the user-space. Storage services on LeapIO are "offload ready;" they can portably run in ARM SoC or on host x86 in a trusted VM. The software overhead only exhibits 2-5% throughput reduction compared to bare-metal performance (still delivering the peak bandwidth

of 0.65 million IOPS on a datacenter SSD). Our current SoC prototype also delivers acceptable performance, 5% further reduction on the server side (and up to 30% on the client) but with more than  $20\times$  cost savings. Overall, LeapIO helps cloud providers cut the storage tax and improve utilization without sacrificing performance.

Finally, we discuss the importance of scalable and extensible research platforms for fostering future full-stack software/hardware storage research. Existing software platforms (*e.g.*, SSD/SoC simulators or emulators) are limited by the types of research they support, outdated, and not scalable. Hardware platforms suffer from wear-out issues and are difficult to use. Thus, it's not an excellent choice for new idea exploration in the early phase neither. We argue that it is a critical time for the storage research community to have a new software-based full-system SSD emulator. To this end, we build FEMU, a software (QEMU-based) NVMe flash emulator. FEMU is cheap (open-sourced), relatively accurate (0.5-38% variance as a drop-in replacement of OpenChannel SSD), scalable (can support 32 parallel channels/chips), and extensible (support internal-only and split-level SSD research). FEMU has been used by researchers from tens of institutions and in classes, demonstrating the urgent need for such a research platform and its success.

## CHAPTER 1

#### INTRODUCTION

In this data era, data is being generated everywhere and we face a more urgent need than ever before to store and process data fast and efficiently. With the exponential growth of data that is expected to reach 175 zettabytes by 2025, cloud storage is increasingly becoming the central hub for data management and processing. Thus, storage research is of crucial importance to the continuity of the data-driven development of the modern world.

Among the many benefits cloud platforms promise, predictable performance and cost-efficiency are two fundamental factors driving the success of modern cloud storage. Specifically, users demand fast access to the data in an economical way. To that end, cloud providers keep improving the storage stack to match the ever-increasing data needs with new techniques. However, under rapid changes in modern cloud storage infrastructure in terms of both software and hardware, new challenges emerge for achieving predictable performance with efficiency.

In more detail, modern data intensive applications and the new wave of computing paradigms (e.g., data analytics, ML, serverless) drive the storage stack to undergo a radical shift towards more feature-rich software designs on top of increasingly heterogeneous architectures. As a result, today's cloud storage stack is extremely heavy-weight and complex, burning 10-20% of data center CPU cycles and introducing severe performance non-determinism (i.e., long tail latencies). Unfortunately, the deployment of new acceleration hardware (e.g., NVMe SSDs and IO co-processors) only partially addresses the problem. Due to the intrinsic complexities and idiosyncrasies in hardware (e.g., NAND Flash management) and lack of system-level support, it remains a challenge to design performant and cost-efficient cloud storage systems. In particular, achieving sub-millisecond level latency predictability in a cost-efficient manner is the new battlefield.

#### 1.1 Thesis Statement

In this dissertation, we seek to answer the question: How should the storage stack evolve to satisfy the increasing needs for low and predictable latencies and cost-efficiency in the context of heavy/unpredictable software stack and heterogeneous architectures? In particular, we make the following thesis statement:

The performance predictability and CPU efficiency challenges associated with modern storage stack can be effectively tackled by cross-layer co-designs across applications/OS and software/hardware boundaries to exploit data redundancy for low and consistent latencies as well as to seamlessly utilize low-cost co-processors for agile storage service offloading, both with small efforts for easy deployment.

To support this statement, in the first part of the dissertation, we explore various novel techniques and designs to achieve predictable latencies across different layers of the storage stack (Chapter 3). In the second part, we think further to design the next-generation offloaded storage stack to target both performance and cost-efficiency (Chapter 4). In the third part, we revisit the lack of proper research platform support for conducting modern storage research (like the ones discussed in the aforementioned parts) and develop a new storage research platform to fill the gap (Chapter 5). In summary, this dissertation will cover the following systems we built:

- MITTOS: An OS that is transparent, exposing its resource busyness to enable applications to achieve millisecond tail tolerance.

- TEAFA: A flash array delivering predictable performance, which uniquely combines a simple yet powerful host-SSD interface to proactively and deterministically reconstruct late requests.

- TTFLASH: A "tiny-tail" flash drive (SSD) that eliminates GC-induced tail latencies by circumventing GC-blocked IOs with several novel strategies.

- FEMU: A software (QEMU-based) flash emulator for fostering future full-stack software/

hardware SSD research, with accuracy, extensibility and scalability.

• **LeapIO:** A new cloud storage stack that leverages ARM-based co-processors to offload complex storage services while satisfying many deployment requirements.

For the rest of the chapter, we will briefly introduce the problems of performance predictability (§1.2) and cost-efficiency (§1.3) in modern storage stack, categorize state-of-the-art approaches and give a high-level overview of our solutions. In §1.4, we summarize the contributions of this dissertation. In §1.5, we introduce the outline for the rest of the dissertation.

## 1.2 Performance Predictability

Low and stable latency is a critical key to the success of many services, but variable load and resource sharing common in cloud environments induce resource contention that in turn produces "the tail latency problem." With flash storage becoming the mainstream destination for storage users, the SSD consumer market continues to grow at a significant rate [17], SSD-backed cloud-VM instances are becoming the norm [14, 15]. From the users' side, they demand fast and stable latencies [143, 160]. However, SSDs do not always deliver the performance that users expect [36]. Some even suggest that flash storage "may not save the world" (due to the tail latency problem) [28]. Some recent works dissect why it is hard to meet Service Level Agreement (SLA) with SSDs [199] and reveal high performance variability in 7 million hours of SSDs deployments [165]. Built on top of flash/SSD, All Flash/SSD Array (AFA) is a popular solution for high-end storage servers [67, 73, 80, 138]. The increasing deployment of real-time analytics and machine learning applications further fuels the growth of AFA market to a predicted \$18 billion market by 2023 [7, 11]. Similarly, large scale flash storage common in large datacenter/cloud storage providers [6, 55, 257] must address users' craving for low and predictable latencies [118, 141].

In this context, tail latency is very important. Many recent SSD products are released and evaluated not just on the average speed but the percentile latencies as well [37, 77, 180]. These all paint

the reality that customers would like SSD products with deterministically stable and low latency. Unfortunately, it's hard to have SSDs deliver stable latencies. The non-deterministic performance comes from the fact that SSDs must perform many internal (background) management activities such as the garbage collection (GC) process, wear leveling, and internal buffer flush [34, 149, 331]. Even a single background write/erase operation will cause the user IOs to be queued (delayed) behind for tens of milliseconds or worse [205, 232, 309]. At the core of flash performance instability is the well-known and "notorious"  $garbage\ collection\ (GC)$  process. A GC operation causes long delays as the SSD cannot serve (blocks) incoming IOs. Due to an ongoing GC, read latency variance can increase by  $100 \times [28, 141]$ . In the last decade, there is a large body of work that reduces the number of GC operations with a variety of novel techniques. However, we find almost no work in literature that attempts to eliminate the blocking nature of GC operations and deliver steady SSD performance in long runs.

#### 1.2.1 Existing Approaches

Due to this problem, many works have been proposed in the last decade to achieve stable latencies, to reduce latency tail. One view of the design space is depicted in Figure 1.1, which we discuss at a high level below.

• White-box (*i.e.*, Use full-knowledge of the hardware for improved performance): This category arguably has the highest number of publications. The lower left of the figure represents pure white-box approaches that assume the SSD firmware can be entirely modified [137, 149, 185, 186, 190, 196, 220, 233, 249, 250, 296, 310, 311, 318, 328]. Many of the techniques here only delay/optimize the GC process but not evade the GC process, thus still far from reducing the tail significantly. Rearchitecting the firmware is also not a desirable option for many commodity SSDs. The upper side of the left region is an entirely host-managed/software-defined flash [56, 126, 164, 170, 222, 257, 279]. Theoretically here the host can be specifically tuned such that the SSD management operations do not interfere with user operations, but host-managed

<sup>\*</sup> Contributions of this dissertation: TEAFA, LeapIO, FEMU, and my contributions to MITTOS, TTFLASH

Figure 1.1: Design space for achieving stable performance on top of modern Flash storage stack. The figure depicts the design space of research in reducing tail latencies. The x-axis represents the three spectrums, white-, gray-, and black-box approaches. Top left: AppFlash [222], DIDACache [283], SDF [257], FlashBlox [170], RAIL [56], Willow [279], LightNVM [126], MittOS [164], IOFlow [297]; Bottom left: AutoSSD [196], BlueDBM [183], LightStore [137], ATLAS [149], KAML [178], PGC [220], FlashShare [328], KVSSD [190], SOML [233], FEMU [228], FLIN [296], TTFLASH [318], GCFreeSSD [185], PaRT-FTL [249], Triple-A [186]; Center: Nameless [330], Harmonia [209], Stream [207], Biscuit [155], TEAFA [229], ActiveFlash [298]; Right: Reflex [211], Decibel [251], LeapIO [227], Hedging [105, 141], C3 [295], F2FS [218], Gecko [286], Purity [138], Rails [292], SWAN [201], SOFA [134].

strategies require "open" devices (*e.g.*, OpenChannel SSDs) that are not as pervasive as commodity SSDs in deployment.