# IODA: A Host/Device Co-Design for Strong Predictability Contract on Modern Flash Storage

Huaicheng Li, Martin L. Putra, Ronald Shi, Xing Lin, Gregory R. Ganger, Haryadi S. Gunawi

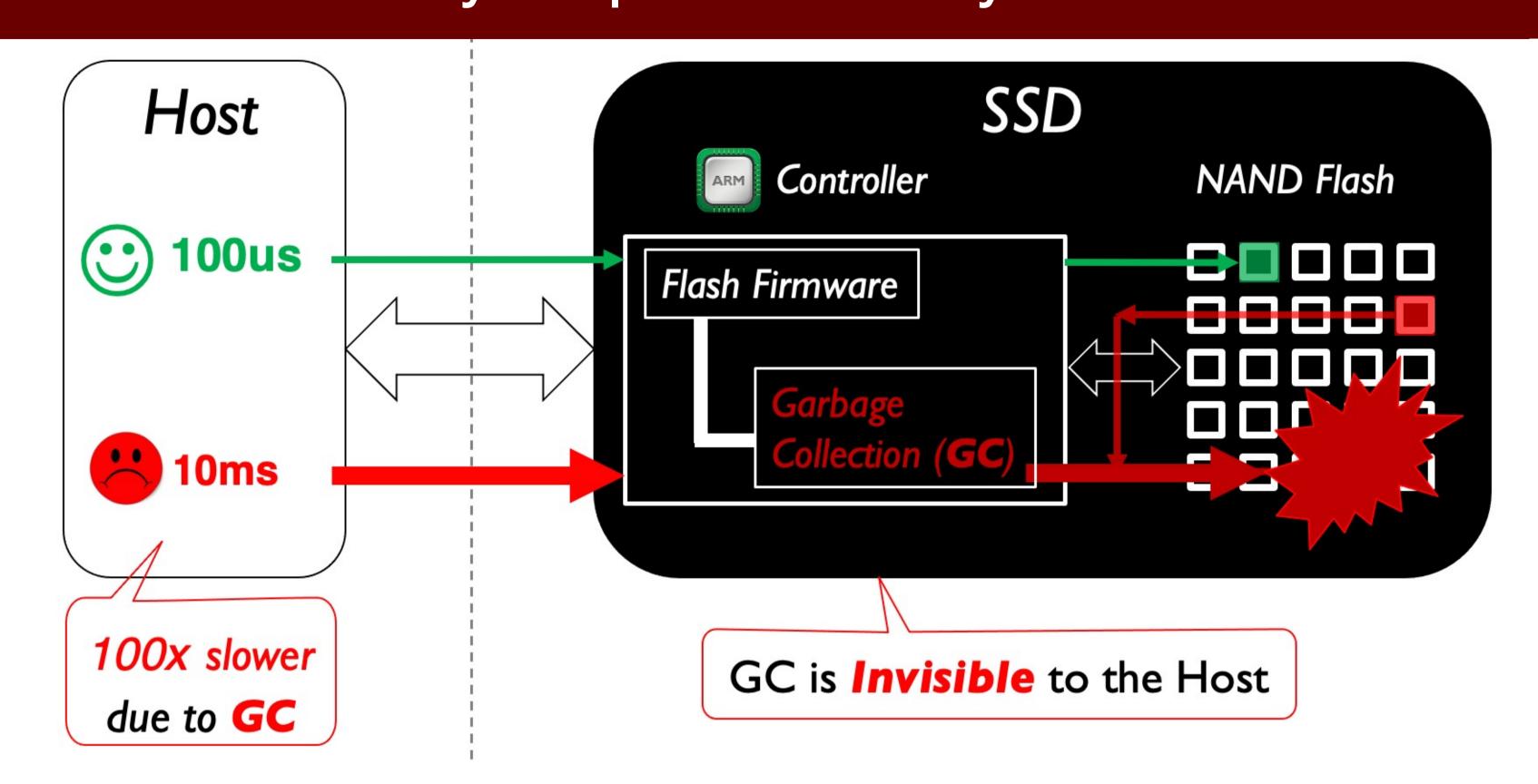

### Latency Unpredictability in SSDs

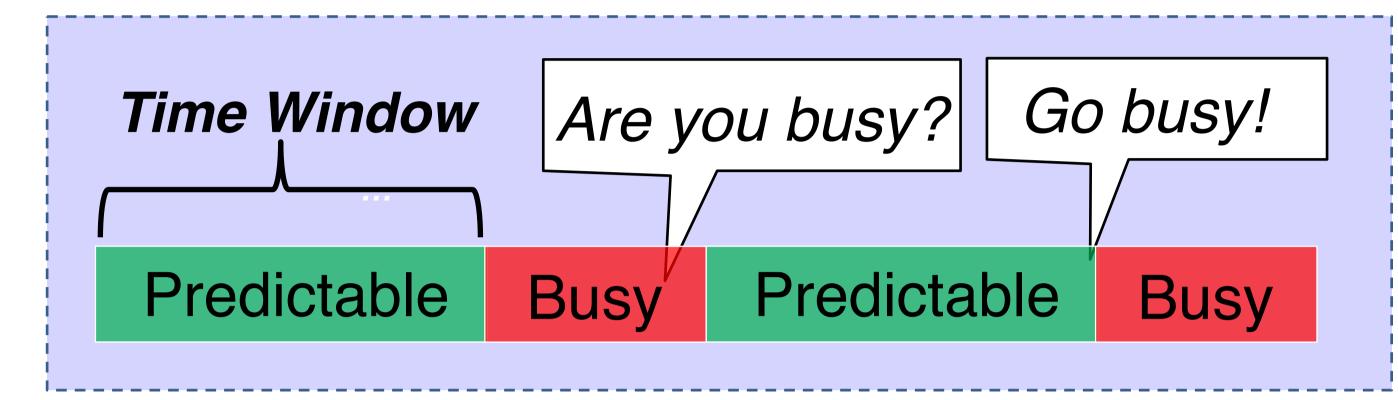

### NVMe Predictable Latency Mode (PLM)

- PLM is a major leap for host/SSD co-design

- Device status query & toggling

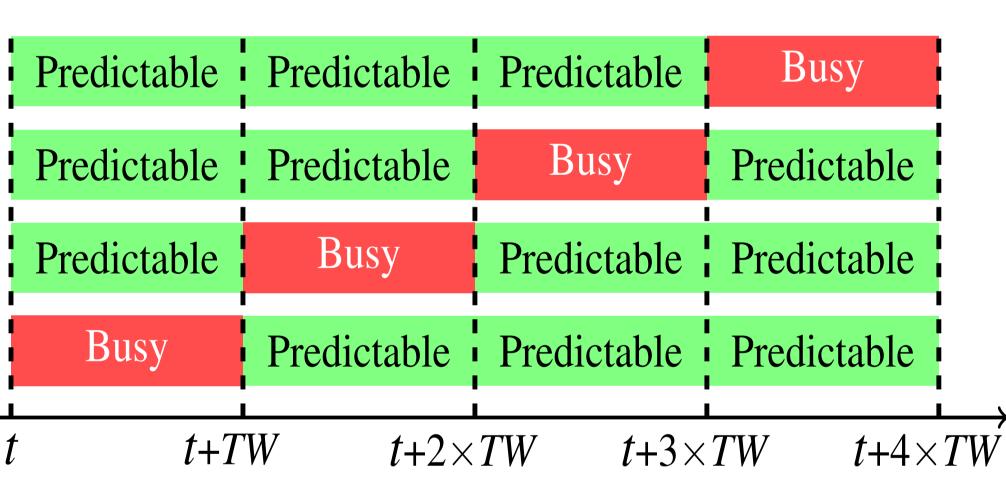

- Predictable/Busy Time Window (TW)

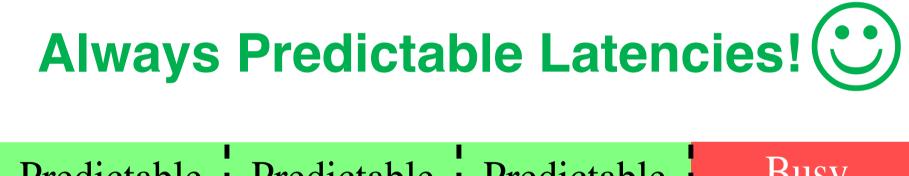

## IODA's Journey for Always-Predictable Latencies

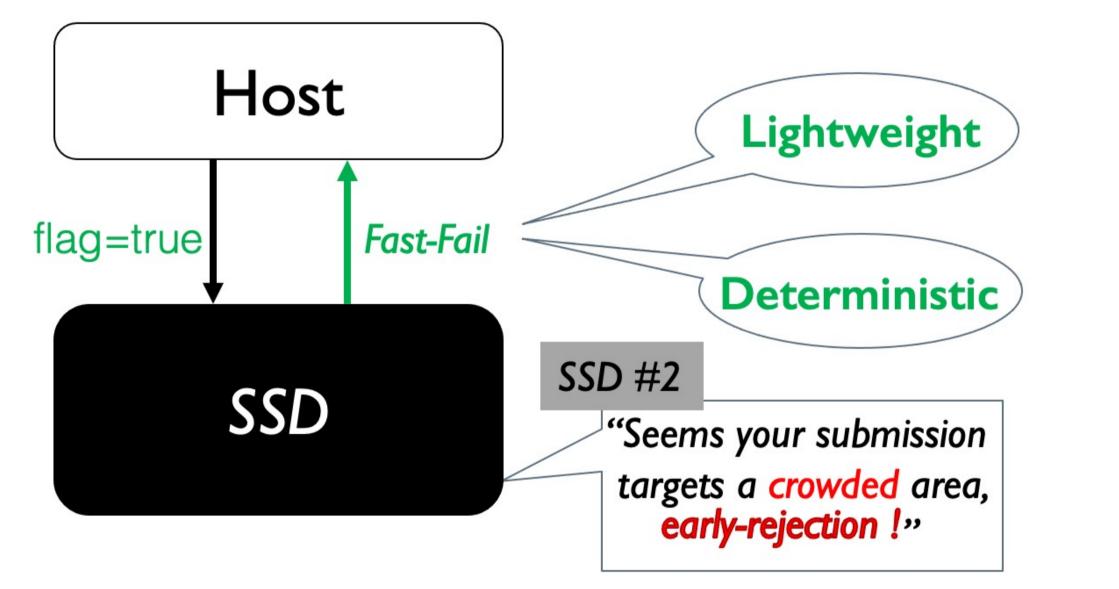

IOD₁: Predictable Latency Flagged I/Os

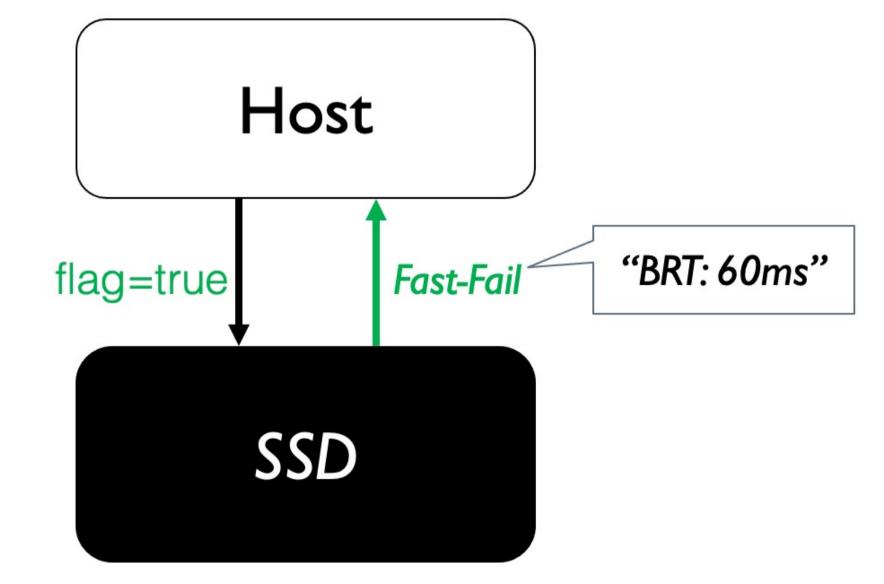

IOD<sub>2</sub>: Busy Remaining Time (BRT)

Piggyback *BRT*: reconstruct data from less busy SSDs (GC; 1 busy SSD at a time!

#### **IODA Busy Latency Windows**

### IODA Evaluation Results

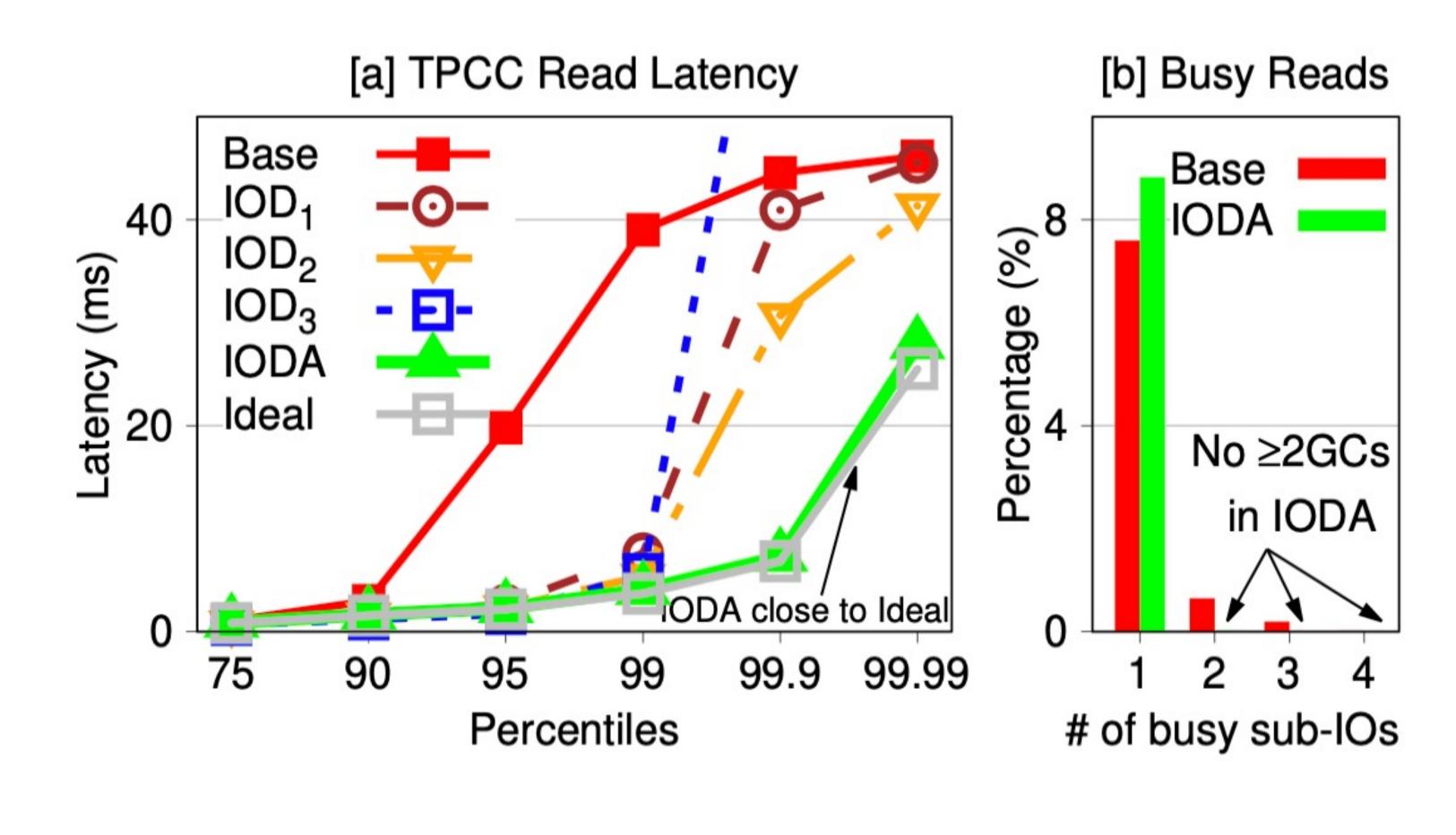

IODA is close to Ideal between P95 and P99.99

IODA successfully eliminates concurrent GCs

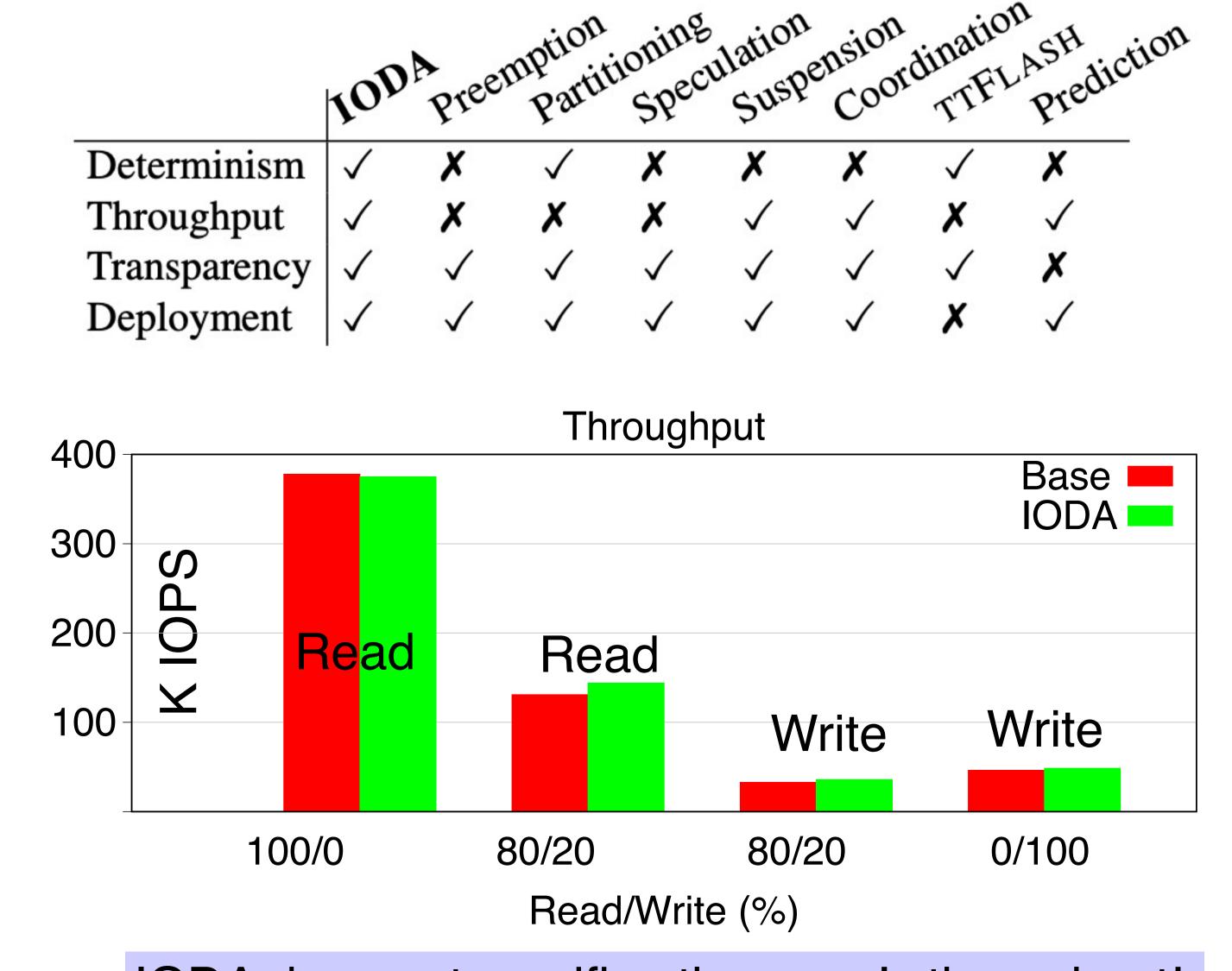

#### Comparison of IODA to state-of-the-art

IODA does not sacrifice the array's throughput!